**PTE**

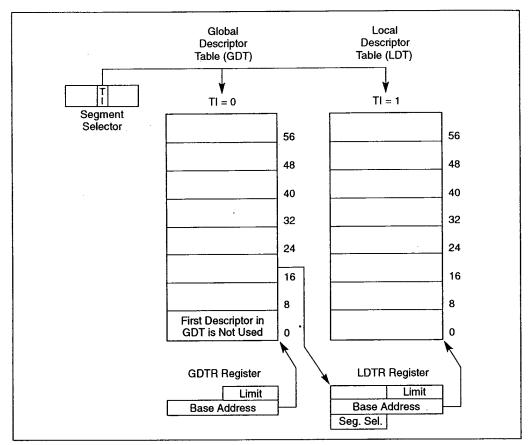

Figure 3-10. Global and Local Descriptor Tables

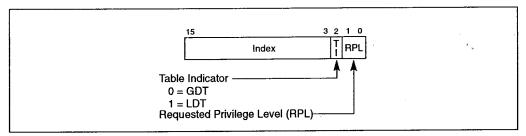

Figure 3-6. Segment Selector

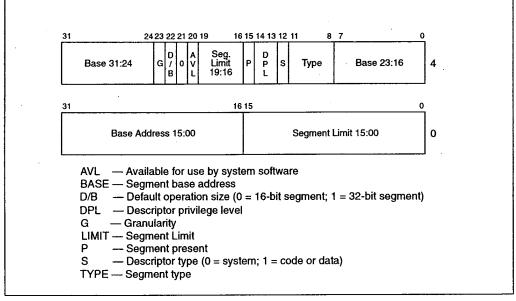

Figure 3-8. Segment Descriptor

### PROTECTED-MODE MEMORY MANAGEMENT

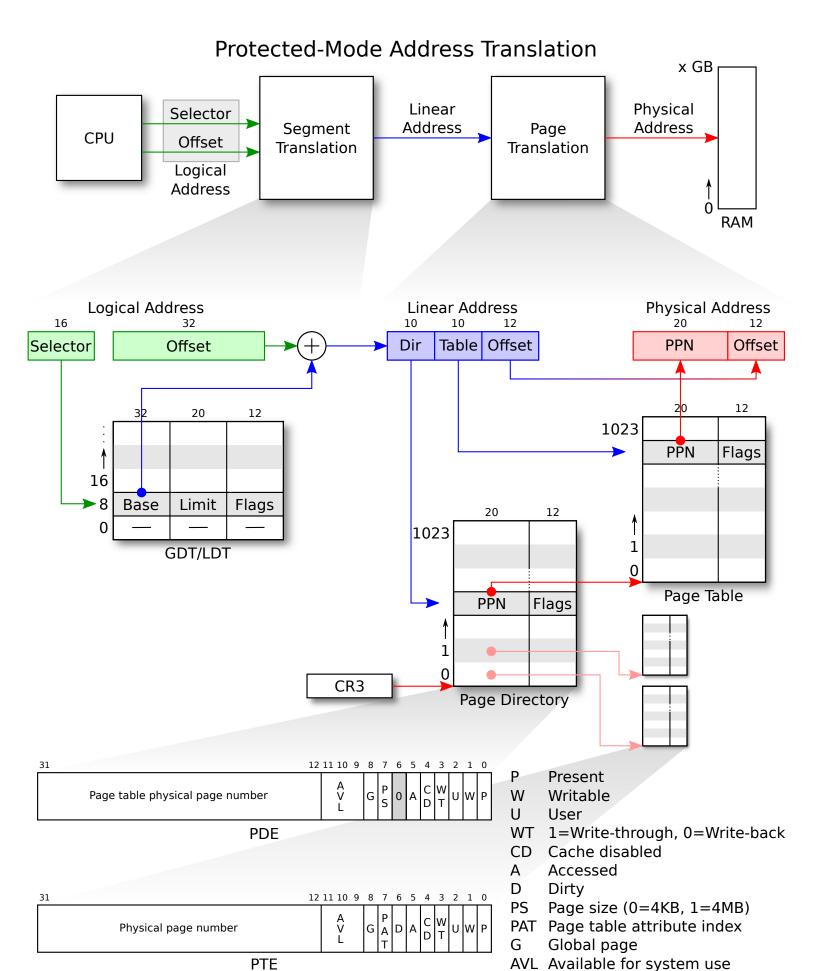

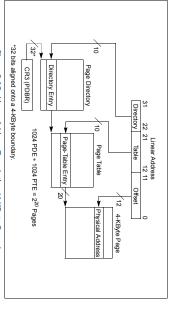

Figure 3-12. Linear Address Translation (4-KByte Pages)

- To select the various table entries, the linear address is divided into three sections:

Page-directory entry Bits 22 through 31 provide an offset to an entry in the page directory. The selected entry provides the base physical address of a page table.

- Page-table entry Bits 12 through 21 of the linear address provide an offset to an entry in the selected page table. This entry provides the base physical address of a page in physical memory.

- ${f Page}$  offset Bits 0 through 11 provides an offset to a physical address in the page.

Memory management software has the option of using one page directory for all programs and tasks, one page directory for each task, or some combination of the two.

## 3.7.2 Linear Address Translation (4-MByte Pages)

Figure 3-13 shows how a page directory can be used to map linear addresses to 4-MByte pages. The entries in the page directory point to 4-MByte pages in physical memory. This paging method can be used to map up to 1024 pages into a 4-GByte linear address space.

3-26 Vol. 3

### PROTECTED-MODE MEMORY MANAGEMENT

interpreted as the 20 most-significant bits of the physical address, which forces pages to be aligned on 4-KByte boundaries.

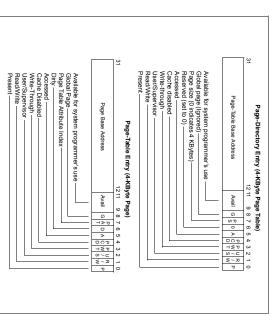

Figure 3-14. Format of Page-Directory and Page-Table Entries for 4-KByte Pages and 32-Bit Physical Addresses

(Page-directory entries for 4-KByte page tables) — Specifies the physical address of the first byte of a page table. The bits in this field are interpreted as the 20 most-significant bits of the physical address, which forces page tables to be aligned on 4-KByte boundaries.

(Page-directory entries for 4-MByte pages) — Specifies the physical address of the first byte of a 4-MByte page. Only bits 22 through 31 of this field are used (and bits 12 through 31 are reserved and must be set to 0, for IA-32 processors through the Pentium II processor). The

Vol. 3 3-29

#### INTERRUPT AND EXCEPTION HANDLING

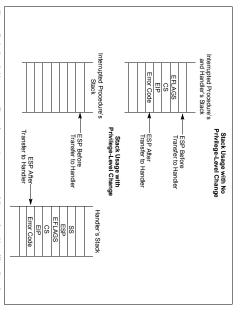

Figure 5-4. Stack Usage on Transfers to Interrupt and Exception-Handling Routines

To return from an exception- or interrupt-handler procedure, the handler must use the IRET (or IRETD) instruction. The IRET instruction is similar to the RET instruction except that it restores the saved flags into the EFLAGS register. The IDPL field of the EFLAGS register is restored only if the CPL is 0. The IF flag is changed only if the CPL is less than or equal to the IDPL. See Chapter 3, "instruction Set Reference, A-M," of the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2A, for a description of the complete operation performed by the IRET instruction.

If a stack switch occurred when calling the handler procedure, the IRET instruction switches back to the interrupted procedure's stack on the return.

# 5.12.1.1 Protection of Exception- and Interrupt-Handler Procedures

The privilege-level protection for exception- and interrupt-handler procedures is similar to that used for ordinary procedure calls when called through a call gate (see Section 4.8.4, "Accessing a Code Segment Through a Call Gate"). The processor does

5-18 Vol. 3

#### INTERRUPT AND EXCEPTION HANDLING

- The RSVD flag indicates that the processor detected 1s in reserved bits of the page directory, when the PSE or PAE flags in control register CR4 are set to 1. Note:

- The PSE flag is only available in recent Intel 64 and IA-32 processors including the Pentium 4, Intel Xeon, P6 family, and Pentium processors

- The PAE flag is only available on recent Intel 64 and IA-32 processors including the Pentium 4, Intel Xeon, and P6 family processors.

- In earlier IA-32 processor, the bit position of the RSVD flag is reserved.

- The I/D flag indicates whether the exception was caused by an instruction fetch. This flag is reserved if the processor does not support execute-disable bit or execute disable bit feature is not enabled (see Section 3.10).

Figure 5-9. Page-Fault Error Code

- The contents of the CR2 register. The processor loads the CR2 register with the 32-bit linear address that generated the exception. The page-fault handler can use this address to locate the corresponding page directory and page-table entries. Another page fault can potentially occur during execution of the page-fault handler; the handler should save the contents of the CR2 register before a second page fault can occur. If a page fault is caused by a page-level protection

- Processors update CR2 whenever a page fault is detected. If a second page fault occurs while an

earlier page fault is being delivered, the faulting linear address of the second rault will overwrite

the contents of RC2 (replacing the previous address). These updates to RC2 occur even if the

page fault results in a double fault or occurs during the delivery of a double fault.

Vol. 3 5-55

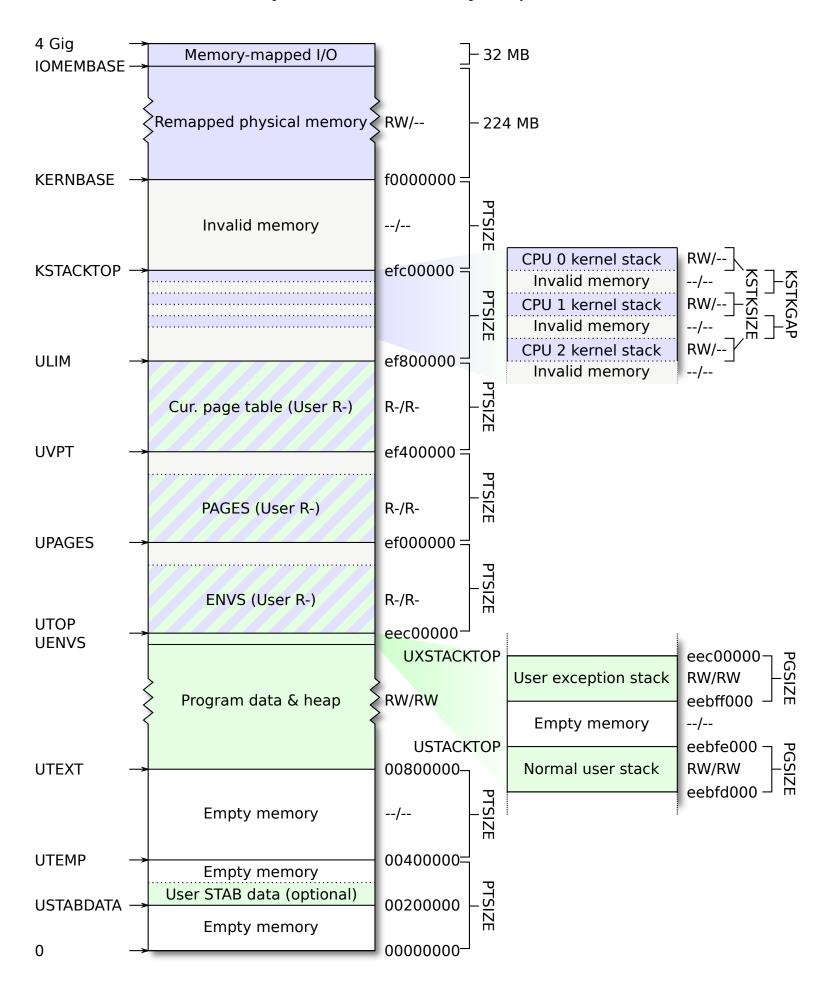

#### JOS Virtual Memory Map