| d'a | 2. x86-64: addresses<br>3. x86-64: page table structure<br>1. TLBs                                                       | etures                                 |                               |

|-----|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------|

| e ( | 5. Where does the OS live?                                                                                               |                                        | 3                             |

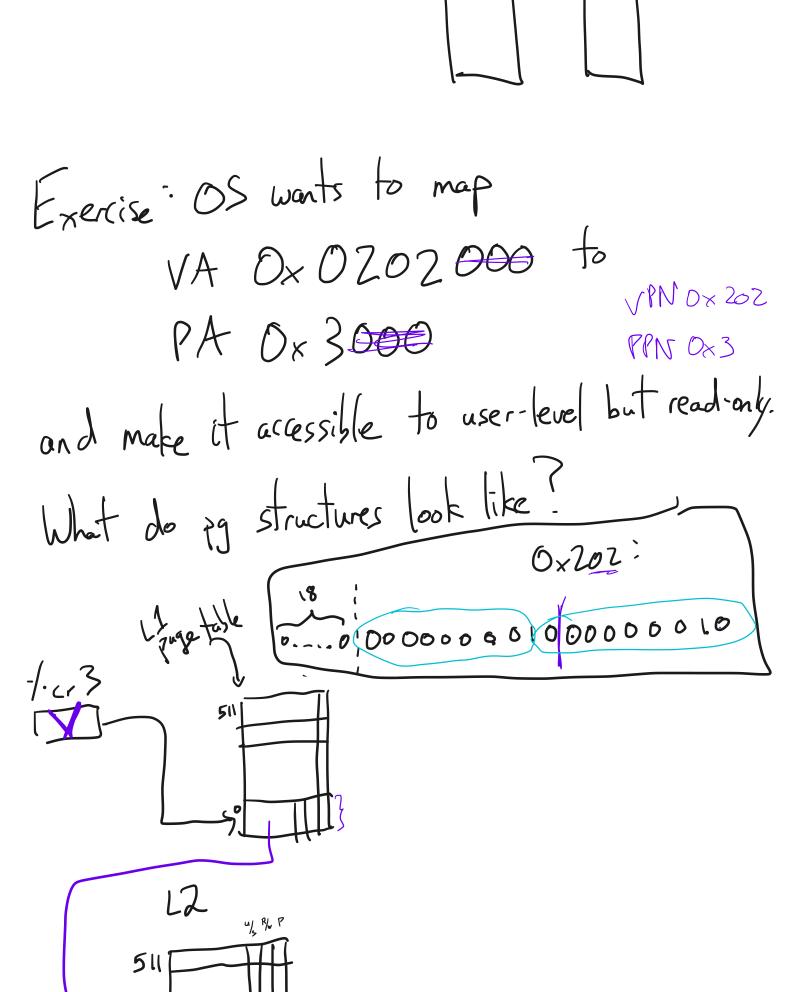

| (.  | Last time - purpose of VM (virtual men - central mechanism: page t - idealized page table: VPN - giant table, PIN is the | asle<br>Vis on index in                | POP tall PPN PPN  Zole at the |

|     | index - thus, pg table implements - in reality, it's a map from                                                          | a map from V<br>n VPN -> PPN U1        | PN->PPN<br>[4], because       |

|     | - NOTE: VPN + PPN do not ne                                                                                              | ecessarily have the                    | same # of                     |

|     | Because the table would be as a linear table. Instead, the                                                               | gigantic, it's not<br>e architecture s | malericlited<br>pecifies      |

M. Last time

2. ×86-64; addresses 264 Sits = 8 bytes VAs: 36 5ths for VPN 1211 48 47 bit 63 [-247, 247-1] Address space has 48 usable bits. 2 possible addresses (each addresses a byte). Thus, 256 TB. 57 bits: 128 PB ,52 bits PAS

| Physical memory can be addressed 7 up to                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52 bits.  How much physical memory can thus be supported?  Additional of the supported? |

| Mapping going from 48-bit number (VA) to 52-bit<br>number (PA) at the granularity of ranges of 22.                                                                                                                                            |

| So it's really a mapping from 36-bit numbers to 40-bit numbers.                                                                                                                                                                               |

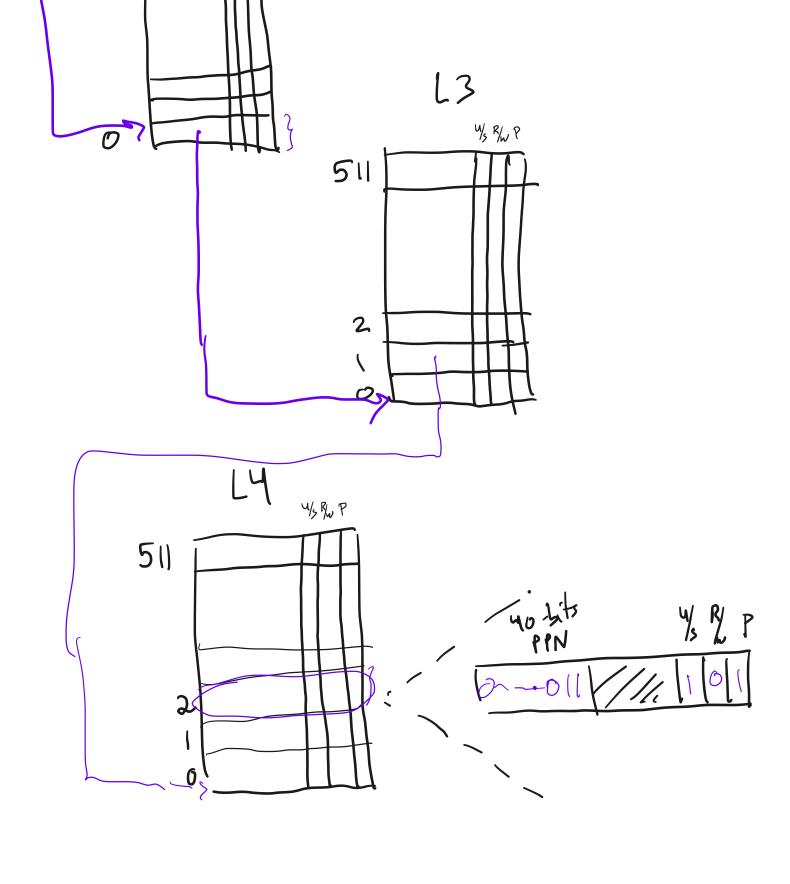

| 3. Page table structures proc table                                                                                                                                                                                                           |

| [see handait] -/-c-3 -/-c-3                                                                                                                                                                                                                   |

4. TLB

< VPN, (PPN, perms) >

< VPN, PTE >

H/v managed: x86, ARM

S/w managed: MITPS

TLB miss ?> ?g fault

Pg fault -> TLB miss

median: 50,5

Mean: 49.9

Max: 95

5 : 23.1

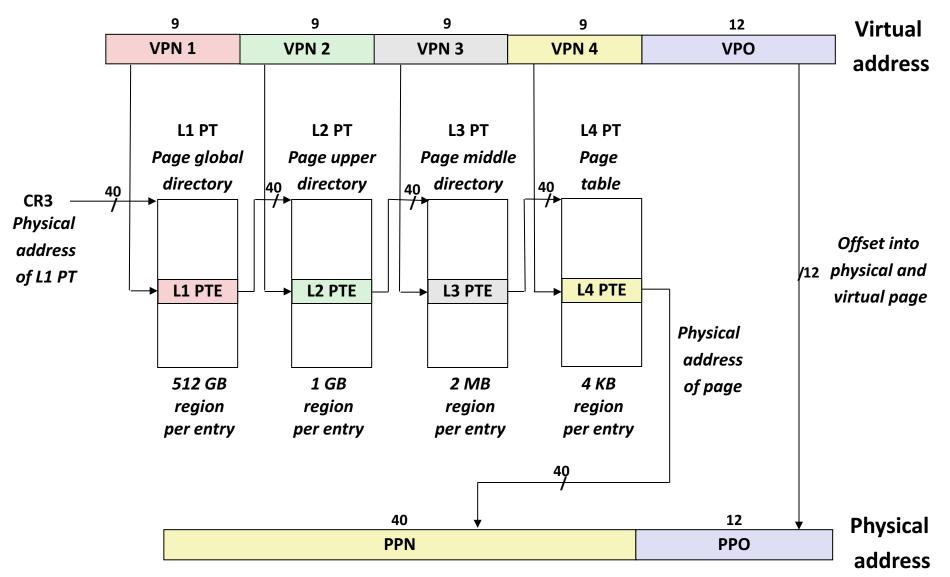

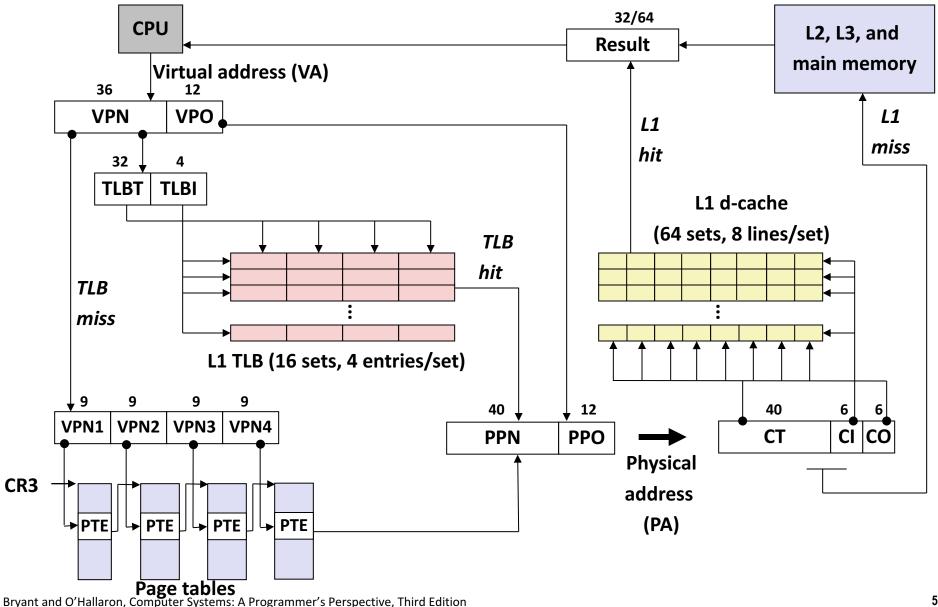

### **Core i7 Page Table Translation**

### **Review of Symbols**

#### Basic Parameters

- N = 2<sup>n</sup>: Number of addresses in virtual address space

- M = 2<sup>m</sup>: Number of addresses in physical address space

- **P = 2**<sup>p</sup> : Page size (bytes)

#### Components of the virtual address (VA)

- TLBI: TLB index

- TLBT: TLB tag

- VPO: Virtual page offset

- VPN: Virtual page number

### Components of the physical address (PA)

- PPO: Physical page offset (same as VPO)

- PPN: Physical page number

- **CO**: Byte offset within cache line

- CI: Cache index

- CT: Cache tag

Const int foo = 5;

$f_{\infty} = 7$

int + bar = ((1) 4 + 0) + + bar = 12;

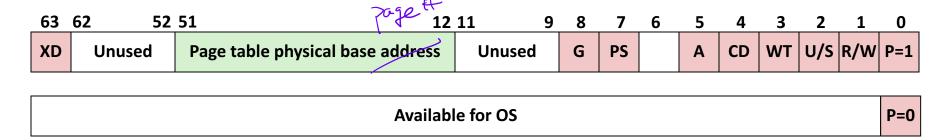

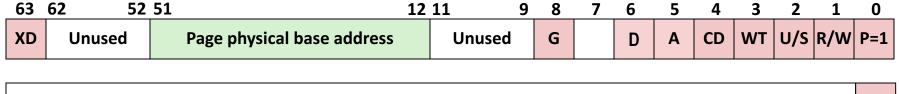

# Core i7 Level 1-3 Page Table Entries

#### Each entry references a 4K child page table. Significant fields:

P: Child page table present in physical memory (1) or not (0).

**R/W:** Read-only or read-write access access permission for all reachable pages.

**U/S:** user or supervisor (kernel) mode access permission for all reachable pages.

**WT:** Write-through or write-back cache policy for the child page table.

**A:** Reference bit (set by MMU on reads and writes, cleared by software).

**PS:** Page size: if bit set, we have 2 MB or 1 GB pages (bit can be set in Level 2 and 3 PTEs only).

**Page table physical base address:** 40 most significant bits of physical page table address (forces page tables to be 4KB aligned)

**XD:** Disable or enable instruction fetches from all pages reachable from this PTE.

### **Core i7 Level 4 Page Table Entries**

Available for OS (for example, if page location on disk)

P=0

#### Each entry references a 4K child page. Significant fields:

P: Child page is present in memory (1) or not (0)

R/W: Read-only or read-write access permission for this page

**U/S:** User or supervisor mode access

WT: Write-through or write-back cache policy for this page

A: Reference bit (set by MMU on reads and writes, cleared by software)

**D:** Dirty bit (set by MMU on writes, cleared by software)

Page physical base address: 40 most significant bits of physical page address (forces pages to be 4KB aligned)

**XD:** Disable or enable instruction fetches from this page.

### **End-to-end Core i7 Address Translation**

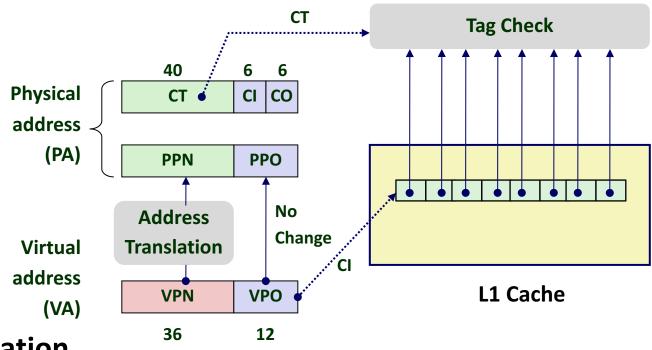

### **Cute Trick for Speeding Up L1 Access**

#### Observation

- Bits that determine CI identical in virtual and physical address

- Can index into cache while address translation taking place

- Cache carefully sized to make this possible: 64 sets, 64-byte cache blocks

- Means 6 bits for cache index, 6 for cache offset

- That's 12 bits; matches VPO,  $PPO \rightarrow$  One reason pages are  $2^{12}$  bits = 4 KB

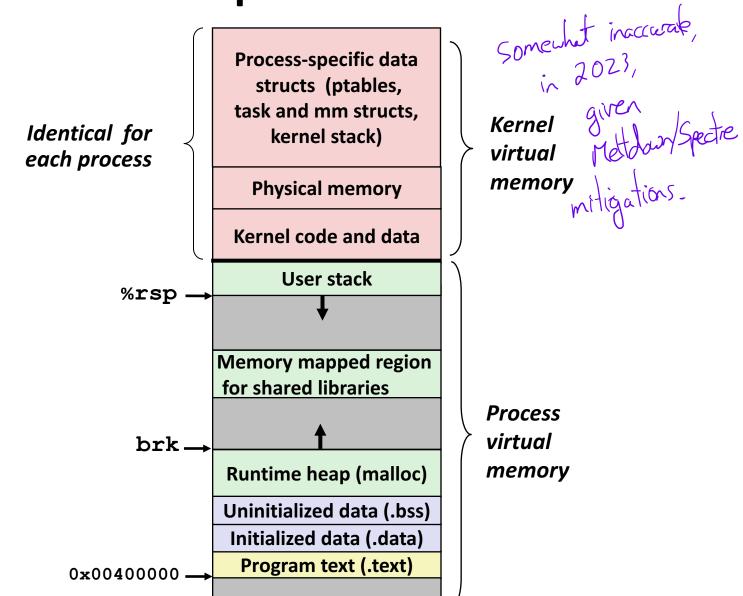

## Virtual Address Space of a Linux Process

Brvant and O'Hallaron, Computer Systems: A Programmer's Perspective,

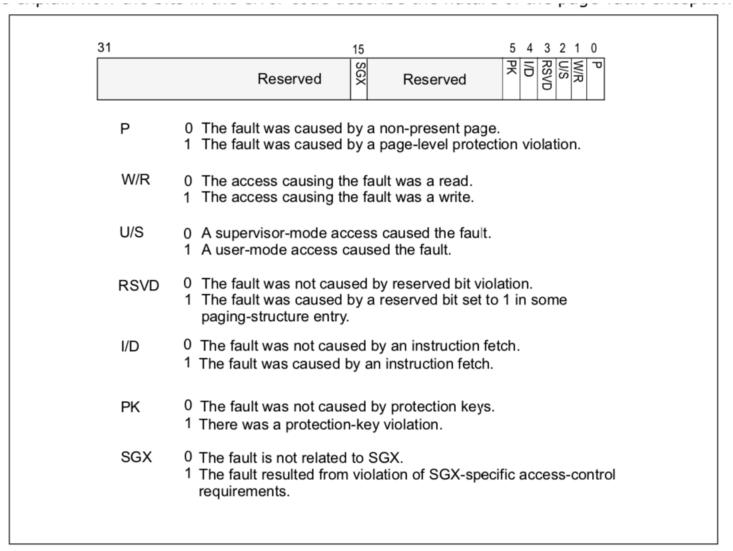

Figure 4-12. Page-Fault Error Code