Q 1, Last time 12. Page faults' intro + mechanics 17 3. Page faults' uses 17 4. Page faults' costs 0 5. Page replacement policies D 6. Thrashing 2. Page faults intro+ mechanics

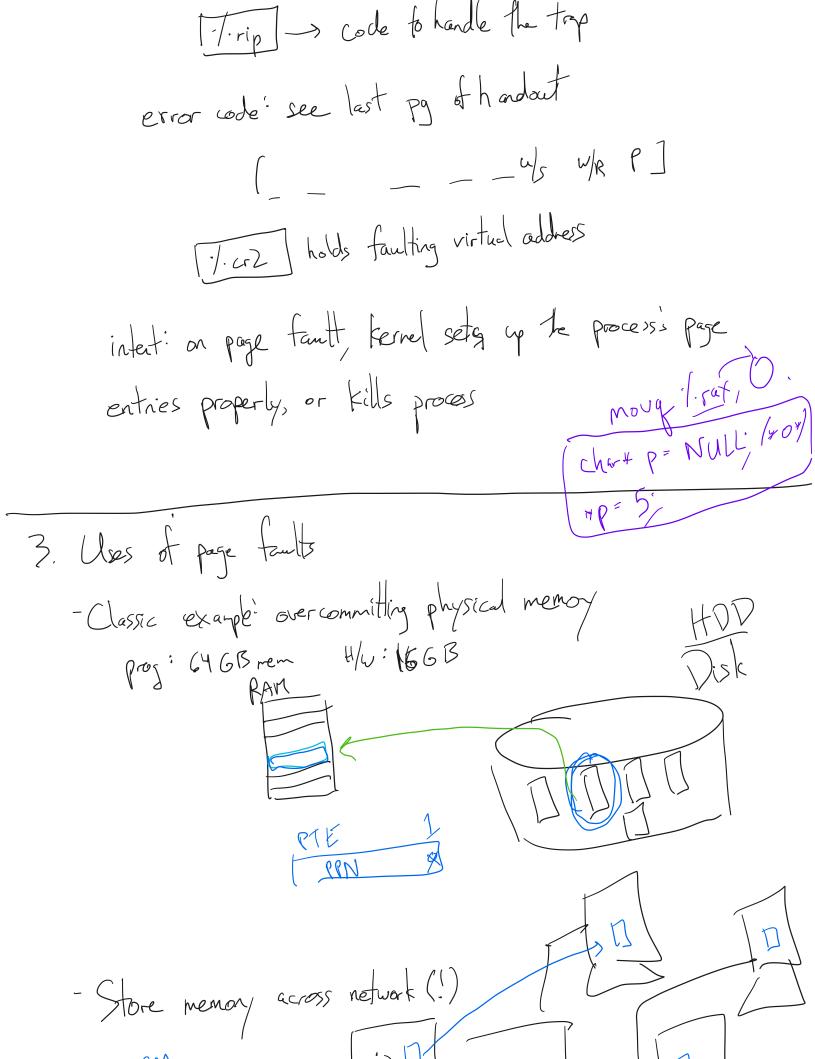

Concept: illegal memory reference: hardware thinks it's illegal (the virtual address might be valid for the process).

OS has to get involved

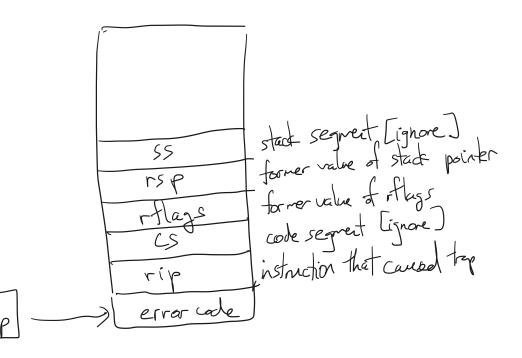

Mechanics:

- processor constructs trap frame and trasfers execution to an interrupt or trap handler

pocess2 process 1 - Accounting / Appel-li (221 - Paging in day to day use - demand paging - growing the stack -BSS page allocation

- Shared text

- Shared libraries

- Shared memory

4. Page faults: costs

look at AMAT (avg. memory access time)

AMAT = (1-p)\* (memory access time) + p+ (page fault time)

p is probability (or frequency) of a page fault

mem access time ~ loons

~ 10 ms = 10 ms disk access fine

QUESTION: what is p s.t. paging hurts performance

by less than 10%.

what paying  $t_m$ The second of the second

5. Page replacement policies

Cache Company Disk

· FIFO: throw out oblest

· MIN (OPT): thou at the enty that want be referred for the largest time.

input: reference story

adput: number of enctions FIFO CABDADBCB phys-slot 51 52 53 7 Sugps, 4 hits ORTIMAL CABDADBCB phy.slot 5] 52 53

Cache site

5 suaps, 6 hits

LRU

ABDADBCB

Phys-slot

\$1

\$2

\$52

\$53

5 swaps, 6 hits

ABCDABCDABCD ABCDABCDABCD BABCDABCD BABCDABCD 12 swaps, Ohths

ABCDABEABCDE

51

52

53

FIFO OPTS LRU Motivaked to implement LRU.

CLOCK

CLOCK

(RUDOPT) scannt

be

informate

informate

printing

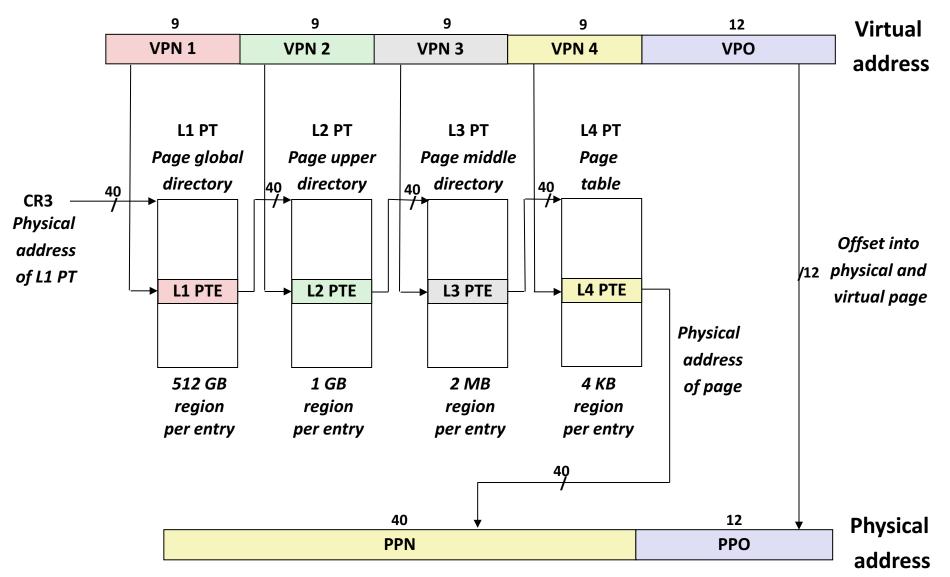

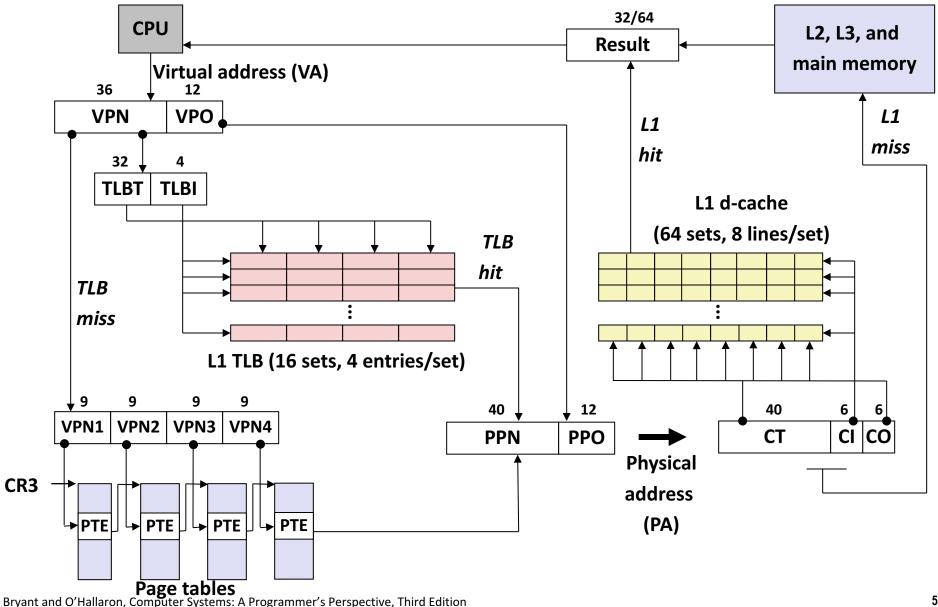

## **Core i7 Page Table Translation**

# **Review of Symbols**

#### Basic Parameters

- N = 2<sup>n</sup>: Number of addresses in virtual address space

- M = 2<sup>m</sup>: Number of addresses in physical address space

- **P = 2**<sup>p</sup> : Page size (bytes)

#### Components of the virtual address (VA)

- TLBI: TLB index

- TLBT: TLB tag

- VPO: Virtual page offset

- VPN: Virtual page number

#### Components of the physical address (PA)

- PPO: Physical page offset (same as VPO)

- PPN: Physical page number

- CO: Byte offset within cache line

- CI: Cache index

- CT: Cache tag

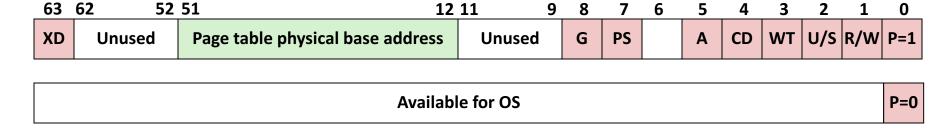

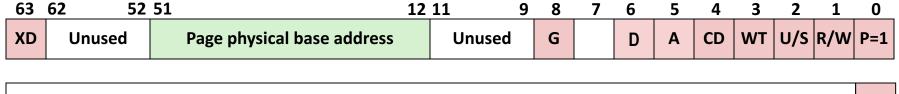

# **Core i7 Level 1-3 Page Table Entries**

#### Each entry references a 4K child page table. Significant fields:

**P:** Child page table present in physical memory (1) or not (0).

**R/W:** Read-only or read-write access access permission for all reachable pages.

**U/S:** user or supervisor (kernel) mode access permission for all reachable pages.

**WT:** Write-through or write-back cache policy for the child page table.

**A:** Reference bit (set by MMU on reads and writes, cleared by software).

**PS:** Page size: if bit set, we have 2 MB or 1 GB pages (bit can be set in Level 2 and 3 PTEs only).

**Page table physical base address:** 40 most significant bits of physical page table address (forces page tables to be 4KB aligned)

**XD:** Disable or enable instruction fetches from all pages reachable from this PTE.

# **Core i7 Level 4 Page Table Entries**

Available for OS (for example, if page location on disk)

P=0

#### Each entry references a 4K child page. Significant fields:

P: Child page is present in memory (1) or not (0)

R/W: Read-only or read-write access permission for this page

**U/S:** User or supervisor mode access

WT: Write-through or write-back cache policy for this page

A: Reference bit (set by MMU on reads and writes, cleared by software)

**D:** Dirty bit (set by MMU on writes, cleared by software)

Page physical base address: 40 most significant bits of physical page address (forces pages to be 4KB aligned)

**XD:** Disable or enable instruction fetches from this page.

### **End-to-end Core i7 Address Translation**

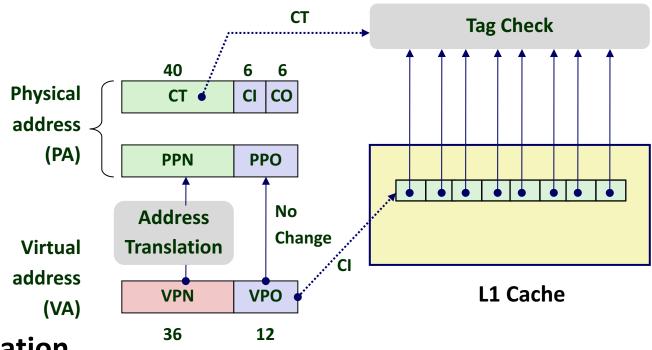

## **Cute Trick for Speeding Up L1 Access**

#### Observation

- Bits that determine CI identical in virtual and physical address

- Can index into cache while address translation taking place

- Cache carefully sized to make this possible: 64 sets, 64-byte cache blocks

- Means 6 bits for cache index, 6 for cache offset

- That's 12 bits; matches VPO,  $PPO \rightarrow$  One reason pages are  $2^{12}$  bits = 4 KB

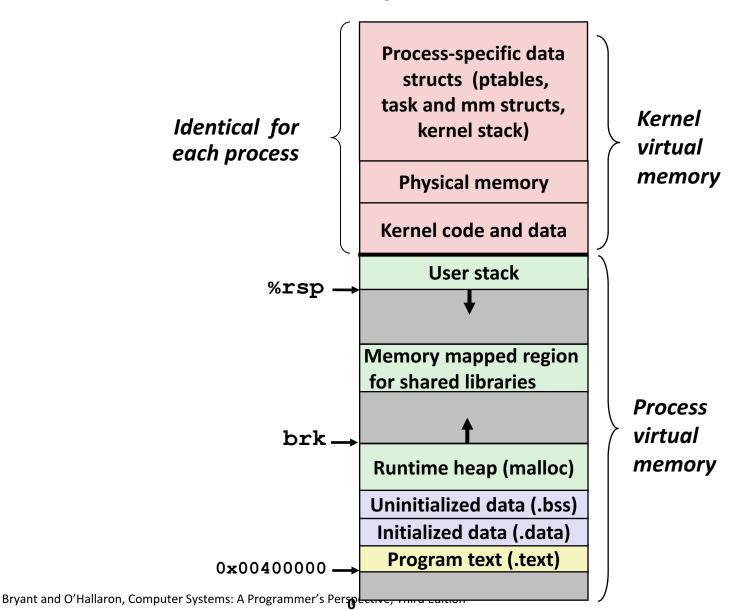

## Virtual Address Space of a Linux Process

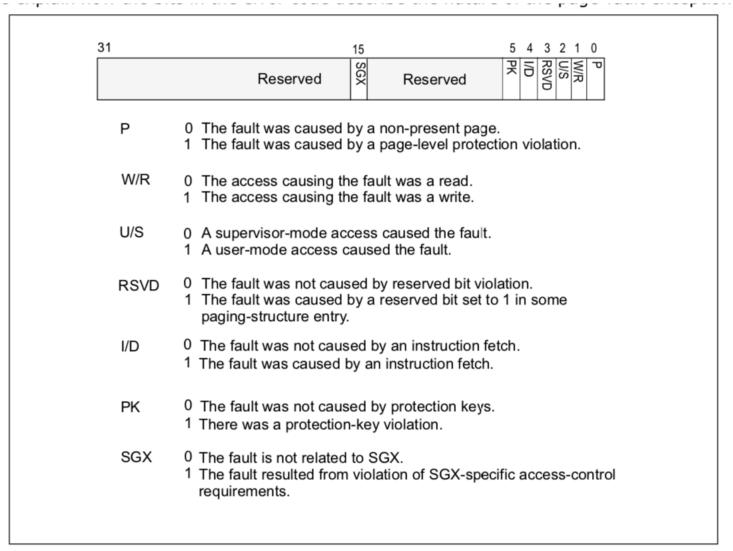

Figure 4-12. Page-Fault Error Code