Operating Systems

================ Start Lecture #17 ================

Note on midterm grades:

The grades on the midterm ranged from 56-95, with a median of 82.

The distribution was

90-100: 4

80-99: 14

70-79: 6

60-69: 3

50-59: 2

Fairly normal except too few high grades, which appears to be

caused by a rather poor showing on resource allocation/deadlock

chapter.

In particular, despite my explicit mention of initial claims in class

and saying something like “If the question include 'safe' the

answer should include 'initial claims'”, and my doing one of

these questions on the practice midterm answers, almost everyone forgot

the initial claims and drew pictures that might or might not be safe.

Midterm letter grades:

Since the midterm is worth four times each lab and only one lab was

graded, I computed the midterm letter grade with the same four to one

ratio. I did not give pluses and minuses, but definitely do for final

grades.

If you did not take the midterm, you received a UE (unable to evaluate).

Several students have not done lab1; this affected their grade.

Review of Midterm exam

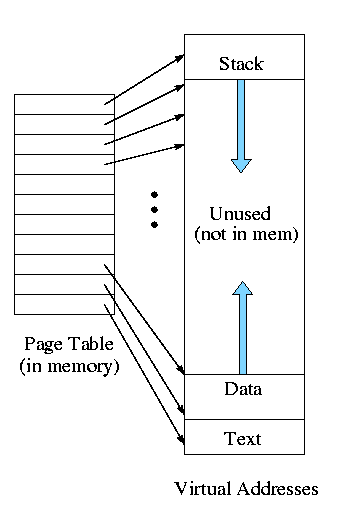

4.3.2: Page tables

A discussion of page tables is also appropriate for (non-demand)

paging, but the issues are more acute with demand paging since the

tables can be much larger. Why?

-

The total size of the active processes is no longer limited to the

size of physical memory. Since the total size of the processes is

greater, the total size of the page tables is greater and hence

concerns over the size of the page table are more acute.

-

With demand paging an important question is the choice of a victim

page to page out. Data in the page table

can be useful in this choice.

We must be able access to the page table very quickly since it is

needed for every memory access.

Unfortunate laws of hardware.

-

Big and fast are essentially incompatible.

-

Big and fast and low cost is hopeless.

So we can't just say, put the page table in fast processor registers,

and let it be huge, and sell the system for $1000.

The simplest solution is to put the page table in main memory.

However it seems to be both too slow and two big.

-

Seems too slow since all memory references require two reference.

-

This can be largely repaired by using a TLB, which is fast

and, although small, often captures almost all references to

the page table.

-

For this course, officially TLBs “do not exist”,

that is if you are asked to perform a translation, you should

assume there is no TLB.

-

Nonetheless we will discuss them below and in reality they

very much do exist.

-

The page table might be too big.

-

Currently we are considering contiguous virtual

addresses ranges (i.e. the virtual addresses have no holes).

-

Typically put the stack at one end of virtual address and the

global (or static) data at the other end and let them grow towards

each other.

-

The virtual memory in between is unused.

-

That does not sound so bad.

Why should we care about virtual memory?

-

This unused virtual memory can be huge (in address range) and

hence the page table (which is stored in real memory

will mostly contain unneeded PTEs.

-

Works fine if the maximum virtual address size is small, which

was once true (e.g., the PDP-11 of the 1970s) but is no longer the

case.

-

The “fix” is to use multiple levels of mapping.

We will see two examples below: two-level paging and

segmentation plus paging.

Contents of a PTE

Each page has a corresponding page table entry (PTE).

The information in a PTE is for use by the hardware.

Why must it be tailored for the hardware and not the OS?

Because it is accessed frequently.

But actually some systems (software TLB reload) do not have hardware access.

Information set by and used by the OS is normally kept in other OS tables.

The page table format is determined by the hardware, so access routines

are not portable.

The following fields are often present.

-

The valid bit. This tells if

the page is currently loaded (i.e., is in a frame). If set, the frame

number is valid.

It is also called the presence or

presence/absence bit. If a page is accessed with the valid

bit unset, a page fault is generated by the hardware.

-

The frame number. This field is the main reason for the

table.

It gives the virtual to physical address translation.

-

The Modified bit. Indicates that some part of the page

has been written since it was loaded. This is needed if the page is

evicted so that the OS can tell if the page must be written back to

disk.

-

The referenced bit. Indicates that some word in the page

has been referenced. Used to select a victim: unreferenced pages make

good victims by the locality property (discussed below).

-

Protection bits. For example one can mark text pages as

execute only. This requires that boundaries between regions with

different protection are on page boundaries. Normally many

consecutive (in logical address) pages have the same protection so

many page protection bits are redundant.

Protection is more

naturally done with segmentation.

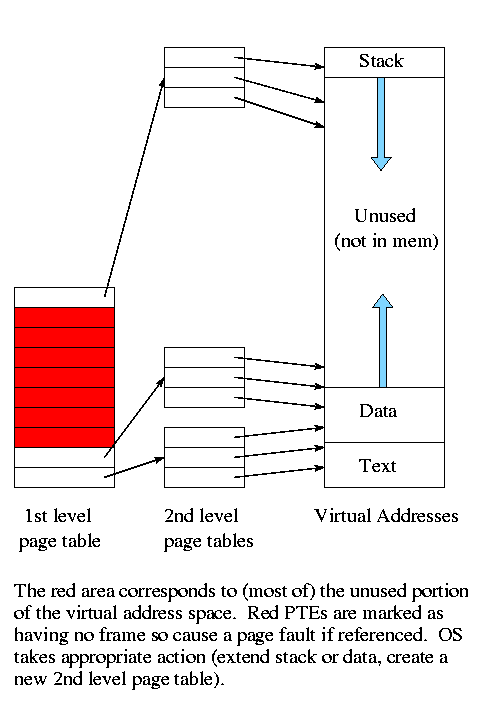

Multilevel page tables (Not on 202 final exam)

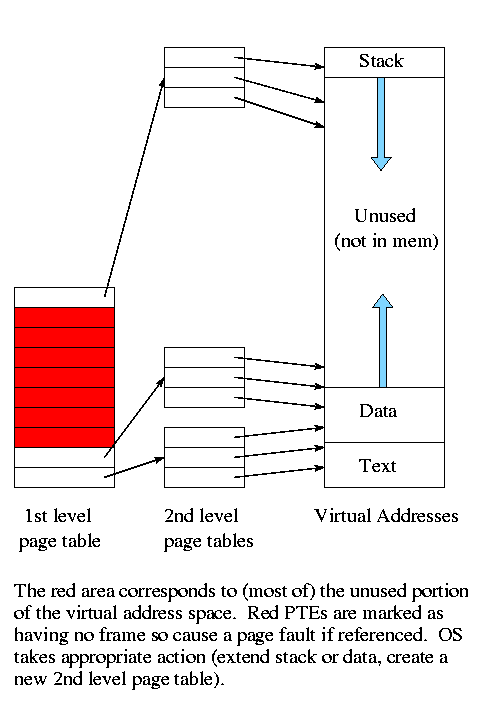

Recall the previous diagram. Most of the virtual memory is the

unused space between the data and stack regions. However, with demand

paging this space does not waste real memory. But the single

large page table does waste real memory.

The idea of multi-level page tables (a similar idea is used in Unix

i-node-based file systems, which we study later when we do I/O) is to

add a level of indirection and have a page table containing pointers

to page tables.

-

Imagine one big page table.

-

Call it the second level page table and

cut it into pieces each the size of a page.

Note that many (typically 1024 or 2048) PTEs fit in one page so

there are far fewer of these pages than PTEs.

-

Now construct a first level page table containing PTEs that

point to these pages.

-

This first level PT is small enough to store in memory. It

contains one PTE for every page of PTEs in the 2nd level PT. A

space reduction of one or two thousand.

-

But since we still have the 2nd level PT, we have made the world

bigger not smaller!

-

Don't store in memory those 2nd level page tables all of whose PTEs

refer to unused memory. That is use demand paging on the (second

level) page table

Address translation with a 2-level page table

For a two level page table the virtual address is divided into

three pieces

+-----+-----+-------+

| P#1 | P#2 | Offset|

+-----+-----+-------+

-

P#1 gives the index into the first level page table.

-

Follow the pointer in the corresponding PTE to reach the frame

containing the relevant 2nd level page table.

-

P#2 gives the index into this 2nd level page table

-

Follow the pointer in the corresponding PTE to reach the frame

containing the (originally) requested frame.

-

Offset gives the offset in this frame where the requested word is

located.

Do an example on the board

The VAX used a 2-level page table structure, but with some wrinkles

(see Tanenbaum for details).

Naturally, there is no need to stop at 2 levels. In fact the SPARC

has 3 levels and the Motorola 68030 has 4 (and the number of bits of

Virtual Address used for P#1, P#2, P#3, and P#4 can be varied).