================ Start Lecture #22

================

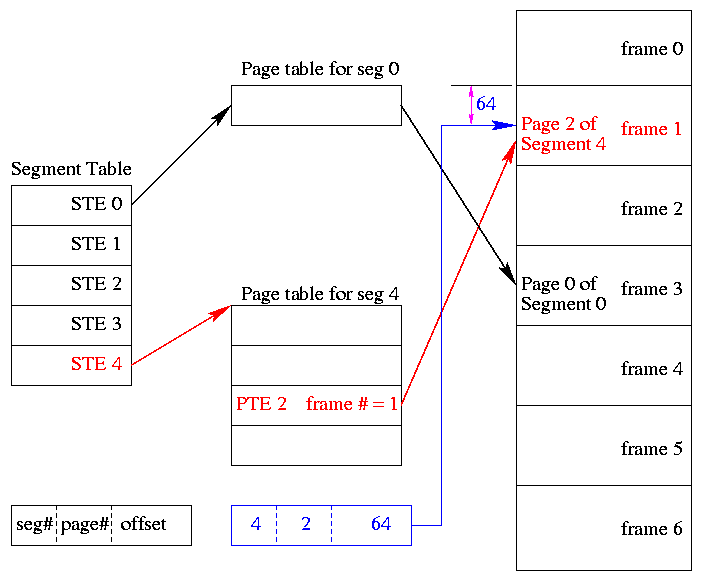

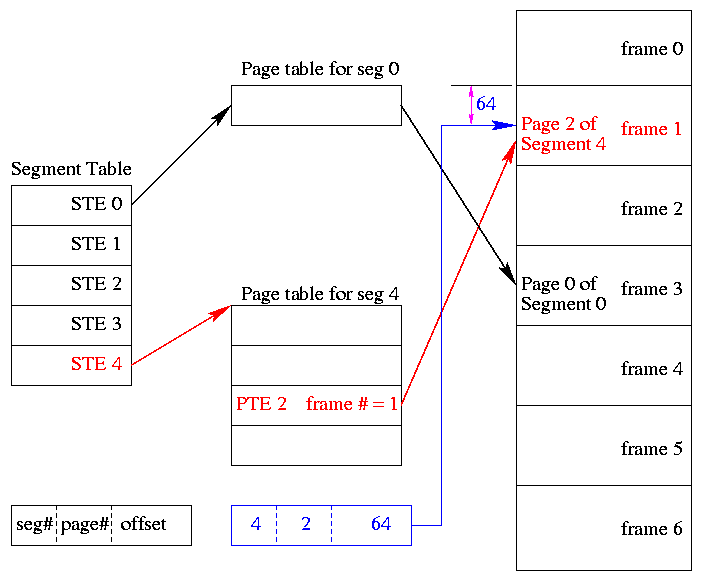

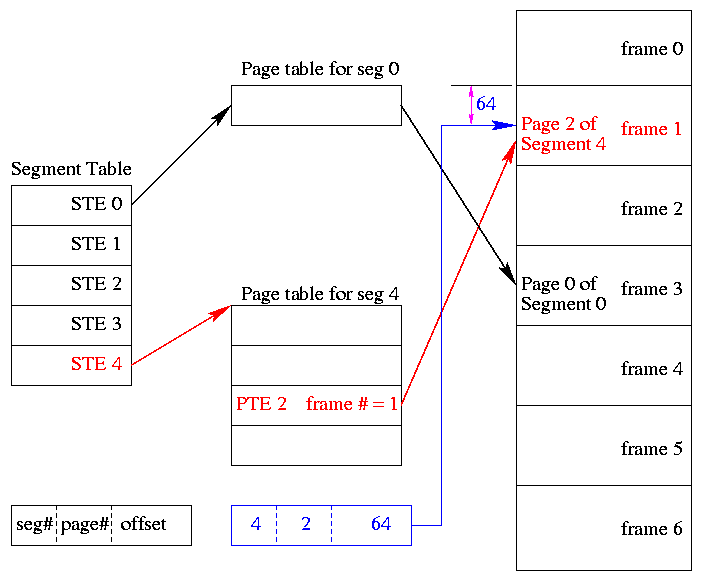

** 4.8.2 and 4.8.3: Segmentation With Paging

(Tanenbaum gives two sections to explain the differences between

Multics and the Intel Pentium. These notes cover what is common to

all segmentation).

Combines both segmentation and paging to get advantages of both at

a cost in complexity. This is very common now.

- A virtual address becomes a triple: (seg#, page#, offset).

- Each segment table entry (STE) points to the page table for that

segment.

Compare this with a

multilevel page table.

- The size of each segment is a multiple of the page size (since the

segment consists of pages). Perhaps not. Can keep the exact size in

the STE (limit value) and shoot the process if it referenced beyond

the limit. In this case the last page of each segment is partially valid.

- The page# field in the address gives the entry in the chosen page

table and the offset gives the offset in the page.

- From the limit field, one can easily compute the size of the

segment in pages (which equals the size of the corresponding page

table in PTEs). Implementations may require the size of a segment to

be a multiple of the page size in which case the STE would store the

number of pages in the segment.

- A straightforward implementation of segmentation with paging

would requires 3 memory references (STE, PTE, referenced word) so a

TLB is crucial.

- Some books carelessly say that segments are of fixed size.

This is wrong.

They are of variable size with a fixed maximum and possibly with the

requirement that the size of a segment is a multiple of the page size.

- The first example of segmentation with paging was Multics.

- Keep protection and sharing information on segments.

This works well for a number of reasons.

- A segment is variable size.

- Segments and their boundaries are user (i.e., linker) visible.

- Segments are shared by sharing their page tables. This

eliminates the problem mentioned above with

shared pages.

- Do replacement on pages so there is no placement question and

no external fragmentation.

- Do fetch-on-demand with pages (i.e., do demand paging).

- In general, segmentation with demand paging works well and is

widely used. The only problems are the complexity and the resulting 3

memory references for each user memory reference. The complexity is

real, but can be managed. The three memory references would be fatal

were it not for TLBs, which considerably ameliorate the problem. TLBs

have high hit rates and for a TLB hit there is essentially no penalty.

Homework: 38.

4.9: Research on Memory Management

Skipped

4.10: Summary

Read

Some Last Words on Memory Management

- Segmentation / Paging / Demand Loading (fetch-on-demand)

- Each is a yes or no alternative.

- Gives 8 possibilities.

- Placement and Replacement.

- Internal and External Fragmentation.

- Page Size and locality of reference.

- Multiprogramming level and medium term scheduling.

Chapter 5: Input/Output

5.1: Principles of I/O Hardware

5.1.1: I/O Devices

- Not much to say. Devices are varied.

- Block versus character devices:

- Devices, such as disks and CDROMs, with addressable chunks

(sectors in this case) are called block

devices,

These devices support seeking.

- Devices, such as Ethernet and modem connections, that are a

stream of characters are called character

devices.

These devices do not support seeking.

- Some cases, like tapes, are not so clear.

5.1.2: Device Controllers

These are the ``devices'' as far as the OS is concerned. That

is, the OS code is written with the controller spec in hand not with

the device spec.

- Also called adaptors.

- The controller abstracts away some of the low level features of

the device.

- For disks, the controller does error checking and buffering.

- (Unofficial) In the old days it handled interleaving of sectors.

(Sectors are interleaved if the

controller or CPU cannot handle the data rate and would otherwise have

to wait a full revolution. This is not a concern with modern systems

since the electronics have increased in speed faster than the

devices.)

- For analog monitors (CRTs) the controller does

a great deal. Analog video is far from a bunch of ones and

zeros.

- Controllers are also called adaptors.

5.1.3: Memory-Mapped I/O

Think of a disk controller and a read request. The goal is to copy

data from the disk to some portion of the central memory. How do we

do this?

- The controller contains a microprocessor and memory and is

connected to the disk (by a cable).

- When the controller asks the disk to read a sector, the contents

come to the controller via the cable and are stored by the controller

in its memory.

- The question is how does the OS, which is running on another

processor, let the controller know that a disk read is desired and how

is the data eventually moved from the controller's memory to the

general system memory.

- Typically the interface the OS sees consists of some device

registers located on the controller.

- These are memory locations into which the OS writes

information such as sector to access, read vs. write, length,

where in system memory to put the data (for a read) or from where

to take the data (for a write).

- There is also typically a device register that acts as a

``go button''.

- There are also devices registers that the OS reads, such as

status of the controller, errors found, etc.

- So now the question is how does the OS read and write the device

register

- With Memory-mapped I/O the device registers

appear as normal memory. All that is needed is to know at which

address each device regester appears. Then the OS uses normal

load and store instructions to write the registers.

- Some systems instead have a special ``I/O space'' into which

the registers are mapped and require the use of special I/O space

instructions to accomplish the load and store. From a conceptual

point of view there is no difference between the two models.

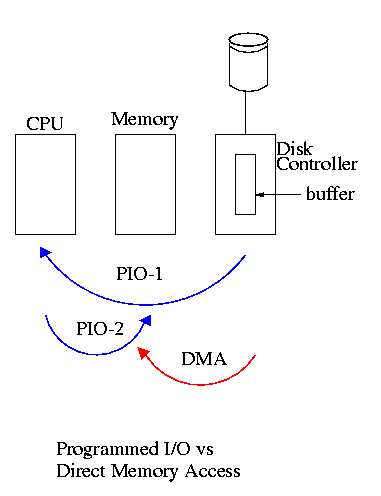

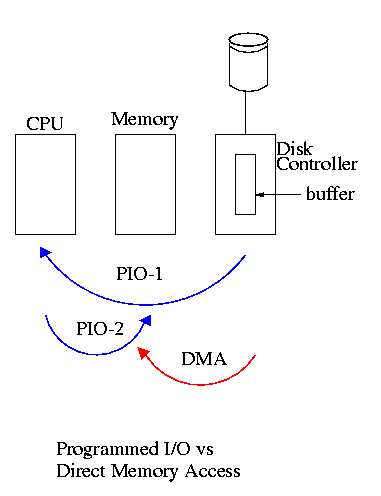

5.1.4: Direct Memory Access (DMA)

- With or without DMA, the disk controller pulls the desired data

from the disk to its buffer (and pushes data from the buffer to the

disk).

- Without DMA, i.e., with programmed I/O (PIO), the

cpu then does loads and stores (or I/O instructions) to copy the data

from the buffer to the desired memory location.

- With a DMA controller, the controller writes the memory without

intervention of the CPU.

- Clearly DMA saves CPU work. But this might not be important if

the CPU is limited by the memory or by system buses.

- Very important is that there is less data movement so the buses

are used less and the entire operation takes less time.

- Since PIO is pure software it is easier to change, which is an

advantage.

- DMA does need a number of bus transfers from the CPU to the

controller to specify the DMA. So DMA is most effective for large

transfers where the setup is amortized.

- Why have the buffer? Why not just go from the disk straight to

the memory.

Answer: Speed matching. The disk supplies data at a fixed rate, which might

exceed the rate the memory can accept it. In particular the memory

might be busy servicing a request from the processor or from another

DMA controller.

Homework: 12