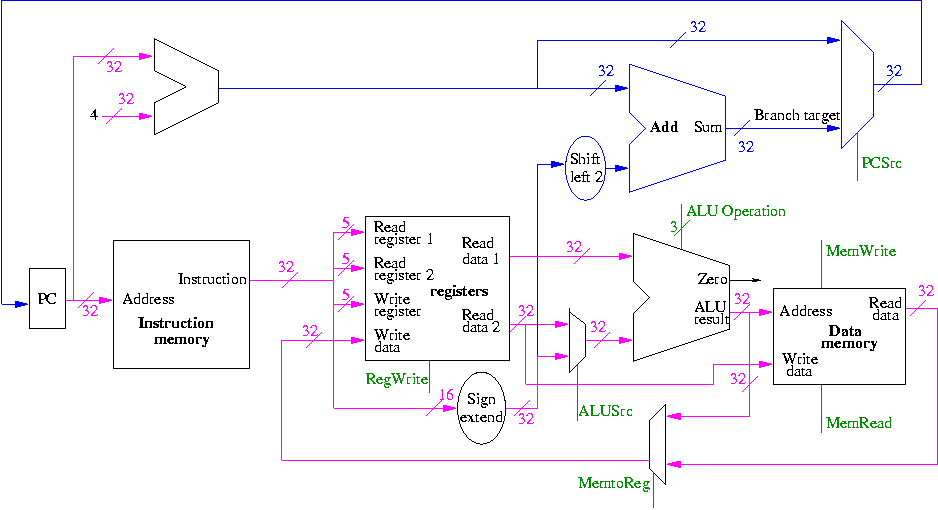

Compare two registers and branch if equal.

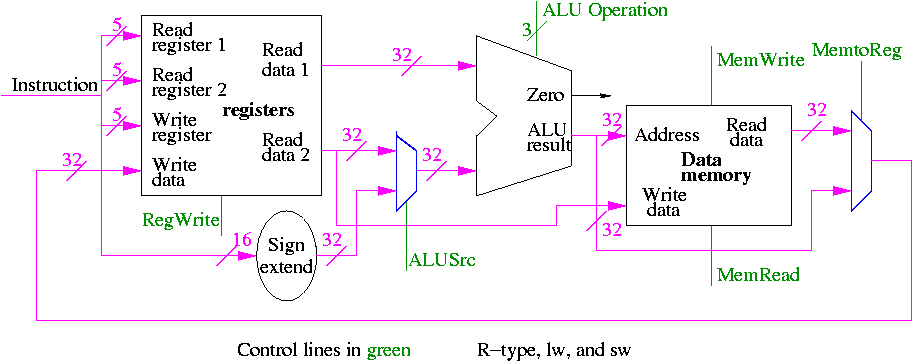

Homework: What would happen if the RegWrite line

had a stuck-at-0 fault (was always deasserted)?

What would happen if the RegWrite line

had a stuck-at-1 fault (was always asserted)?

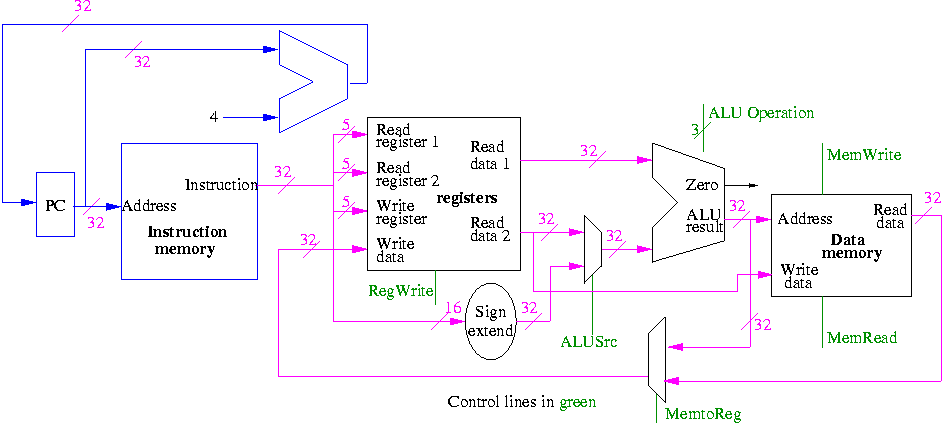

We will just put the pieces together and then figure out the control lines that are needed and how to set them. We are not now worried about speed.

We are assuming that the instruction memory and data memory are separate. So we are not permitting self modifying code. We are not showing how either memory is connected to the outside world (i.e. we are ignoring I/O).

We have to use the same register file with all the pieces since when a load changes a register a subsequent R-type instruction must see the change, when an R-type instruction makes a change the lw/sw must see it (for loading or calculating the effective address, etc.

We could use separate ALUs for each type but it is easy not to so we will use the same ALU for all. We do have a separate adder for incrementing the PC.

The problem is that some inputs can come from different sources.

We will deal with the first two now by using a mux for each. We will deal with the third shortly by (surprise) using a mux.

This is quite easy

We need to have an ``if stmt'' for PC (i.e., a mux)

Homework: 5.5 (just the datapath, not the control), 5.8 (just the datapath, not the control), 5.9.