Computer Architecture

1999-2000 Fall

MW 3:30-4:45

Ciww 109

======== START LECTURE #27

========

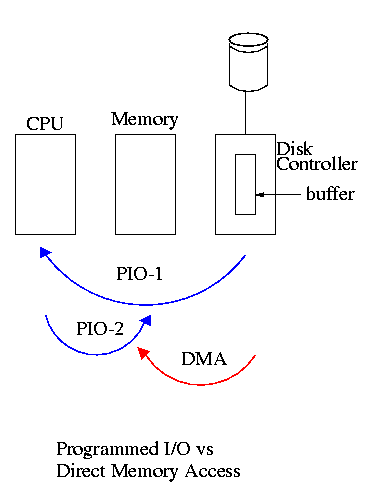

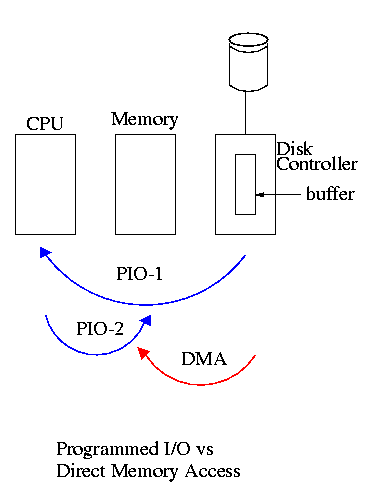

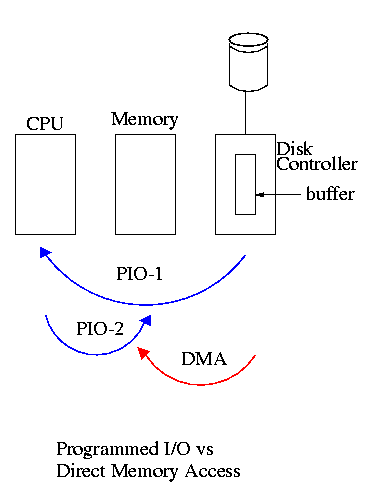

Direct Memory Access (DMA)

The processor initiates the I/O operation then ``something else''

takes care of it and notifies the processor when it is done (or if an

error occurs).

- Have a DMA engine (a small processor) on the controller.

- The processor initiates the DMA by writing the command into data

registers on the controller (e.g., read sector 5, head 4, cylinder

123 into memory location 34500)

- For commands that are longer than the size of the data register(s), a

protocol must be used to transmit the information.

- (I/O done by the processor as in the previous methods is called

programmed I/O, PIO).

- The controller collects data from the device and then sends it on

the bus to the memory without bothering the CPU.

- So we have a multimaster bus and need some sort of

arbitration.

- Normally the I/O devices are given higher priority than the CPU.

- Freeing the CPU from this task is good but isn't as wonderful

as it seems since the memory is busy (but cache hits can be

processed).

- A big gain is that only one bus transaction is needed per bus

load. With PIO, two transactions are needed: controller to

processor and then processor to memory.

- This was for an input operation (the controller writes to

memory). A similar situation occurs for output where the controller

reads from the memory). Once again one bus transaction per bus

load.

- When the controller detects that the I/O is complete or if an

error occurs, it sets the status register accordingly and sends an

interrupt to the processor to notify the latter that the I/O is complete.

More Sophisticated Controllers

- Sometimes called ``intelligent'' device controlers, but I

prefer not to use anthropomorphic terminology.

- Some devices, for example a modem on a serial line, deliver data

without being requested to. So a controller may need to be prepared

for unrequested data.

- Some devices, for example an ethernet, have a complicated

protocol so it is desirable for the controller to process some of that

protocol. In particular, the collision detection and retry with

exponential backoff characteristic of (non-switched) ethernet

requires a real program.

- Hence some controllers have microprocessors on

board that handle much more than block transfers.

- In the old days there were I/O channels, which would execute

programs written dynamically by

the main processor. For the modern controllers, the programs are fixed

and loaded in ROM or PROM.

Subtlties involving the memory system

- Having the controller simply write to memory doesn't update the

cache. Must at least invalidate the cache line.

- Having the controller simply read from memory gets old values with

a write-back cache. Must force writebacks.

- The memory area to be read or written is specified by the program

using virtual addresses. But the I/O must actually go to physical

addresses. Need help from the MMU.