The class did well on the midterm. Although the exam was not very difficult, I am delighted the class did well. The only bad part is that the few students who did not do well need to study more as the final certainly won't be easier. I will go over the exam in a few minutes when more students have arrived. The median grade was 87 and the breakdown was

90-100 18 80-89 14 70-79 8 60-69 2 50-59 1

Lab2 is due on Wednesday

End of Notes.

Homework: 5.5 and 5.8 (control, we already did the datapath), 5.1, 5.2, 5.10 (just the single-cycle datapath) 5.11.

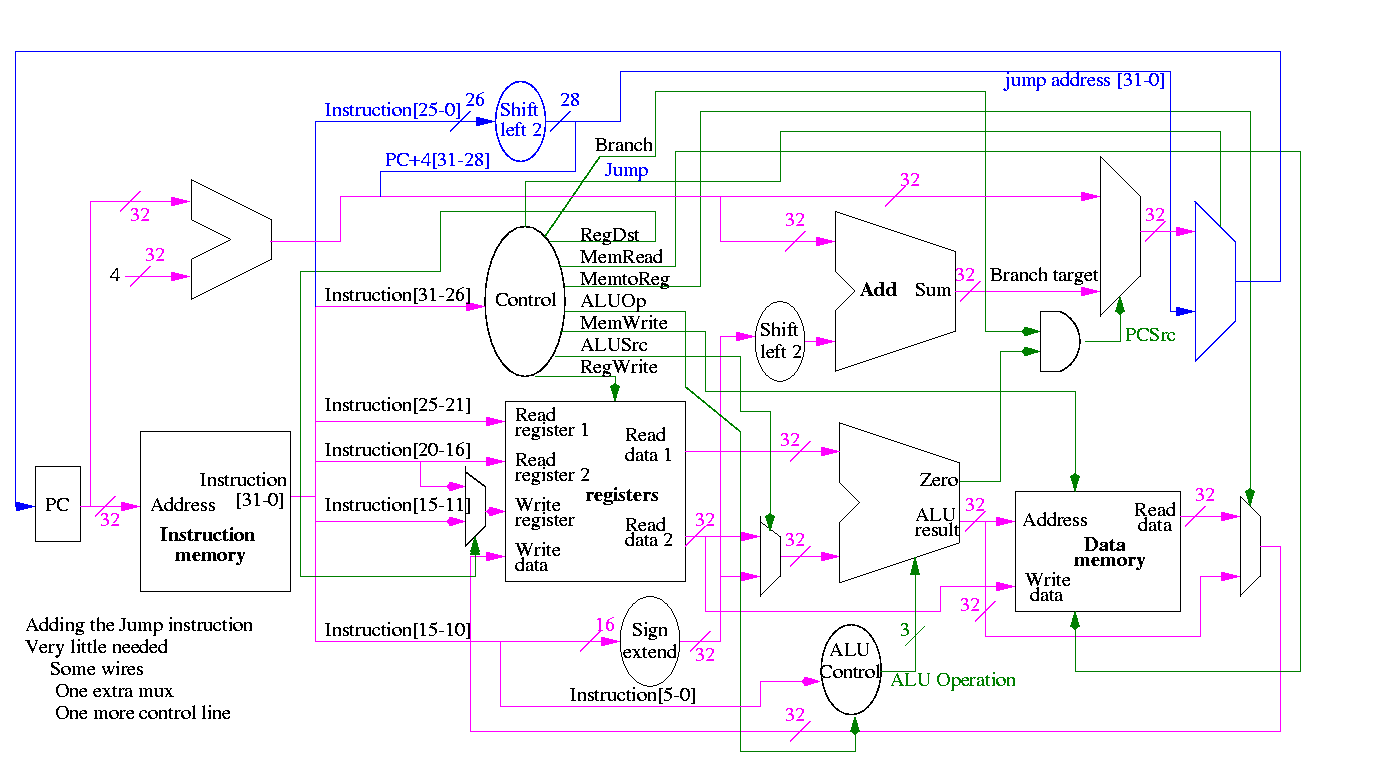

opcode addr

31-26 25-0

Addr is word address; bottom 2 bits of PC are always 0

Top 4 bits of PC stay as they were (AFTER incr by 4)

Easy to add.

Smells like a good final exam type question.

Some instructions are likely slower than others and we must set the clock cycle time long enough for the slowest. The disparity between the cycle times needed for different instructions is quite significant when one considers implementing more difficult instructions, like divide and floating point ops. Actually, if we considered cache misses, which result in references to external DRAM, the cycle time ratios can approach 100.

Possible solutions