======== START LECTURE #26

========

Improving Bus Performance

These improvements mostly come at the cost of increased expense and/or

complexity.

- Hierarchy of buses.

- Synchronous instead of asynchronous protocols.

- Synchronous is actually simplier, but it essentially implies a

hierarchy of protocols since not all devices can operate at the

same speed.

- Wider data path: Use more wires, send more at once.

- Separate address and data lines: Same as above.

- Block transfers: Permit a single transaction to transfer more than

one busload of data. Saves the time to release and acquire the bus,

but the protocol is more complex.

- Obtaining bus access:

- The simplest scheme is to permit only one bus

master.

- That is on each bus only one device is permited to

initiate a bus transaction.

- The other devices are slaves that only

respond to requests.

- With a single master, there is no issue of arbitrating

among multiple requests.

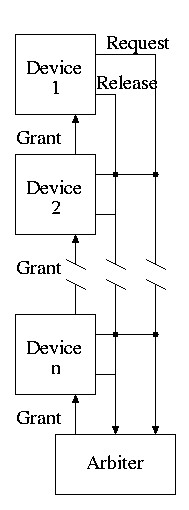

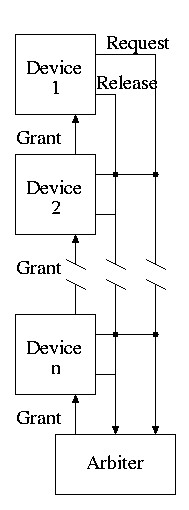

- One can have multiple masters with daisy

chaining of the grant line.

- Any device can raise the request line.

- The device with the request raises the release line when

done.

- The arbiter monitors the request and request lines and

raises the grant line.

- The grant signal is passed from one to the other so the

devices near the arbiter have priority and can starve the ones

further away.

- Passing the grant from device to device takes time.

- Simple but not fair or high performance

- Centralized parallel arbiter: Separate request lines from each

device and separate grant lines. The arbiter decides which device

should be granted the bus.

- Distributed arbitration by self-selection: Requesting

processes identify themselves on the bus and decide individually

(and consistently) which one get the grant.

- Distributed arbitration by collision detection: Each device

transmits whenever it wants, but detects collisions and retries.

Ethernet uses this scheme (but not new switched ethernets).

| Option | High performance | Low cost |

|---|

| bus width | separate address and data lines |

multiplex address and data lines |

| data width | wide | narrow |

| transfer size | multiple bus loads | single bus loads |

| bus masters | multiple | single |

| clocking | synchronous | asynchronous |

Do on the board the example on pages 665-666