======== START LECTURE #8

========

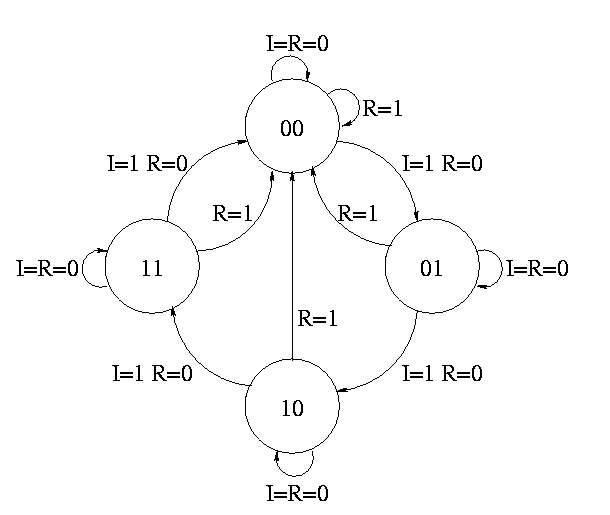

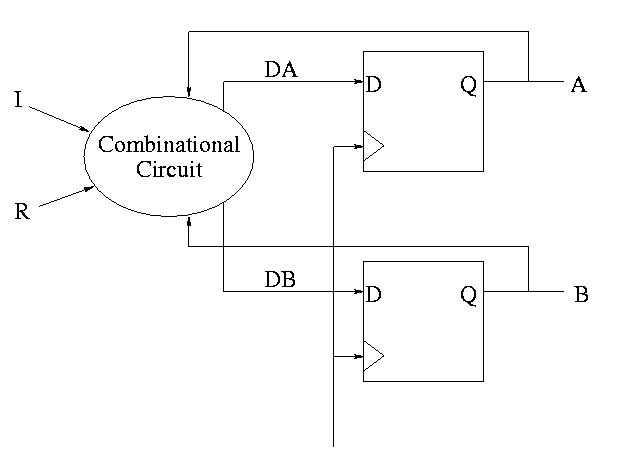

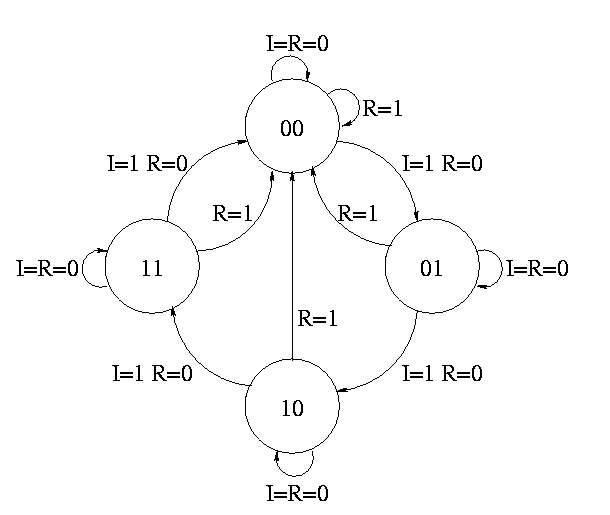

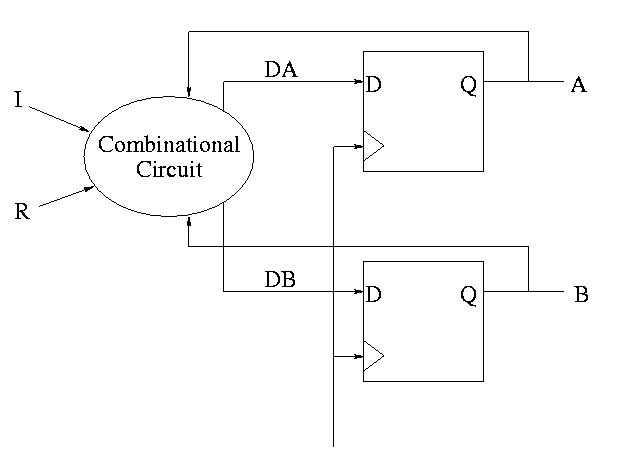

How about a two bit counter.

- State diagram has 4 states 00, 01, 10, 11 and transitions from one

to another

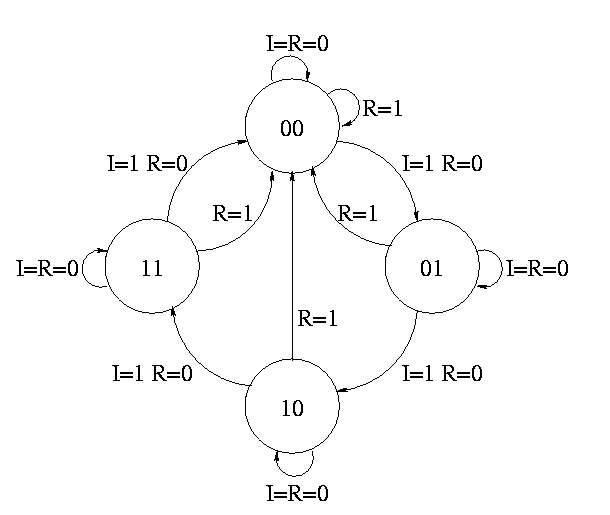

- The circuit diagram has 2 D flops

To determine the combinationatorial circuit we could preceed as before

Current Next ||

A B I R A B || DA DB

------------------++------

This would work but we can instead think about how a counter works and

see that.

DA = R'(A XOR I)

DB = R'(B XOR AI)

Homework: 23

B.6: Finite State Machines

Skipped

B.7 Timing Methodologies

Skipped

Chapter 1

Homework:

READ chapter 1. Do 1.1 -- 1.26 (really one matching question)

Do 1.27 to 1.44 (another matching question),

1.45 (and do 7200 RPM and 10,000 RPM),

1.46, 1.50

Chapter 3

Homework:

Read sections 3.1 3.2 3.3

3.4 Representing instructions in the Computer (MIPS)

Register file

- We just learned how to build this

- 32 Registers each 32 bits

- Register 0 is always 0 when read and stores to register 0 are ignored

Homework:

3.2

R-type instruction (R for register)

op rs rt rd shamt funct

6 5 5 5 5 6

The fields are quite consistent

- op is the opcode

- rs,rt are source operands

- rd is destination

- shamt is the shift amount

- funct is used for op=0 to distinguish alu ops

- alu is arithmetic and logic unit

- add/sub/and/or/not etc.

Example: add $1,$2,$3

- Machine format: 0--2--3--1--0--21

- op=0, alu op

- funct=21 specifies add

- reg1 <-- reg2 + reg3

- the regs can be the same (doubles the value in the reg)

- Do sub by just changing the funct

- If regs are the same, clears the register

I-type (why I?)

op rs rt address

6 5 5 16

- rs is a source reg

- rt is the destination reg

- Transfers to/from memory, normally in words (32-bits)

- But the machine is byte addressible!

- Then how come have load/store word instead of byte?

- Ans: It has load/store byte as well, but we don't cover it.

- What if the address is not a multiple of 4:

- Ans: An error (MIPS requires aligned accesses).

lw/sw $1,addr($2)

- machine format is: op 2 1 addr

- $1 <-- Mem[$2+addr]

$1 --> Mem[$2+addr]

RISC-like properties of the MIPS architecture

- Instructions of the same length

- Field sizes of R-type and I-type correspond.

- The type (R-type, I-type, etc.) is determined by the opcode

- Note that rs is the ref to memory for both load and store

- These properties will prove helpful when we construct a MIPS processor.

Branching instruction

slt (set less-then)

- R-type

- Slt $3,$8,$2

- reg3 <-- (if reg8 < reg2 then 1 else 0)

- Like other R-types: read 2nd and 3rd reg, write 1st

beq and bne (branch (not) equal)

- I-type

- beq $1,$2,L

- if reg1=reg2 then goto L

- bne $1,$2,L

- if reg1!=reg2 then goto L

blt (branch if less than)

- I-type

- blt $5,$8,L

- if reg5 < reg8 then goto L

- *** WRONG ***

- There is no blt instruction.

- Instead use

stl $1,$5,$8

bne $1,$0,L

ble (branch if less than or equal)

- There is no ``ble $5,$8,L'' instruction.

- Note that $5<=$8 <==> NOT ($8<$5)

- Hence we test for $8<$5 and branch if false

stl $1,$8,$5

beq $1,$0,L

bgt (branch if greater than>

- There is no ``bgt $5,$8,L'' instruction.

- Note that $5>$8 <==> $8<$5

- Hence we test for $8<$5 and branch if true

stl $1,$8,$5

bne $1,$0,L

bge (branch if greater than or equal>

- There is no ``bge $5,$8,L'' instruction.

- Note that $5>=$8 <==> NOT ($5<$8)

- Hence we test for $5<$8 and branch if

stl $1,$5,$8

beq $1,$0,L

Note:

Please do not make the mistake of thinking that

stl $1,$5,$8

beq $1,$0,L

is the same as

stl $1,$8,$5

bne $1,$0,L

The negation of X < Y is not Y < X

Homework:

3.12-3.17

J-type instructions (J for jump)

op address

6 26

j (jump)

- J type

- Range is 2^26 words = 1/4 GB

jr (jump register)

- R type, but only one register

- Will it be one of the source registers or the destination register?

- Ans: This will be obvious when we construct the processor

jal (jump and link)

- Used for subroutine calls

- J type

- return address is stored in register 31

I type instructions (revisited)

- The I is for immediate

- These instructions have an immediate third operand,

i.e., the third operand is contained in the instruction itself.

- This means the operand itself and not just its address or register

number are contained in the instruction

addi (add immediate)

addi $1,$2,100

Why is there no subi?

Ans: Make the immediate operand negative.

slti (set less-than immediate)

slti $1,$2,50