======== START LECTURE #6

========

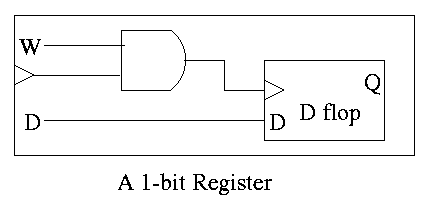

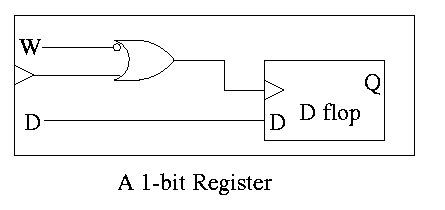

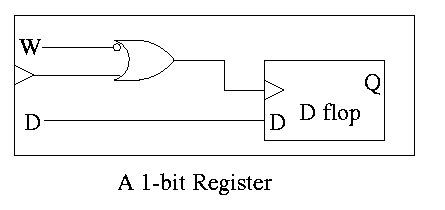

Registers

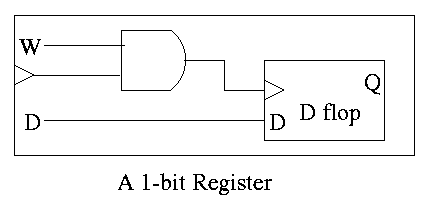

- Basically just an array of D flip-flops

- But what if you don't want to change the register during a

particular cycle?

- Introduce another input, the write line

- The write line is used to ``gate the clock''

- The book forgot the write line.

- Clearly if the write line is high forever, the clock input to

the register is passed right along to the D flop and hence the

input to the register is stored in the D flop when the active edge

occurs (for us the falling edge).

- Also clear is that if the write line is low forever, the clock

to the D flop is always low so has no edges and no writing occurs.

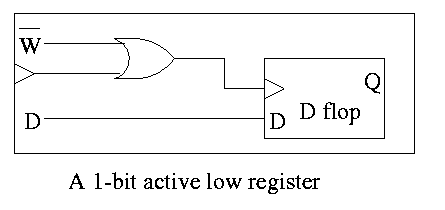

- But what about changing the write line?

- Assert or deassert the write line while the clock is low and

keep it at this value until the clock is low again.

- Not so good! Must have the write line correct quite a while

before the active edge. That is you must know whether you are

writing quite a while in advance.

- Better to do things so the write line must be correct when the

clock is high (i.e., just before the active edge

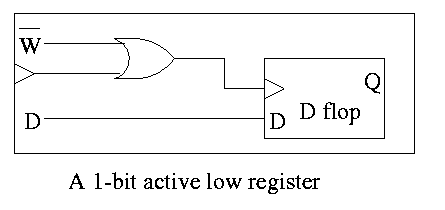

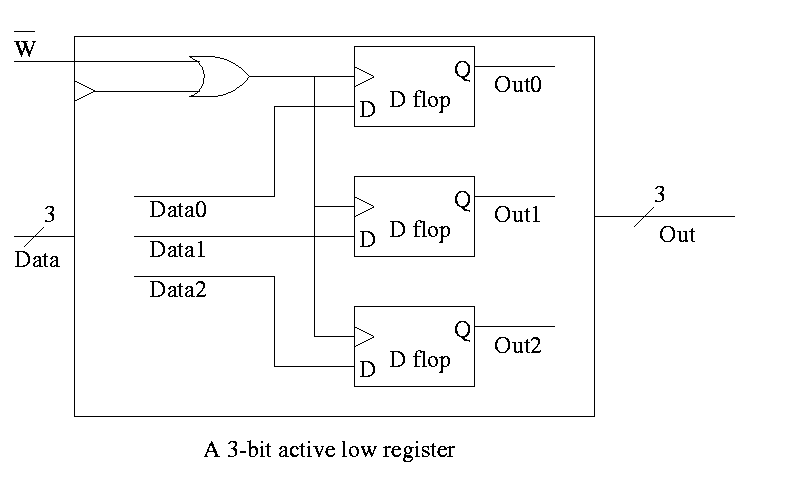

- An alternative is to use an active low write line,

i.e. have a W' input.

- Must have write line and data line valid during setup and hold

times

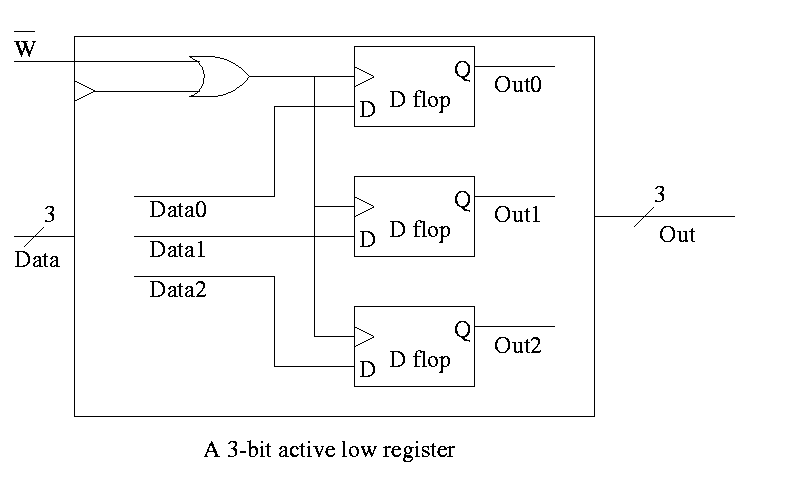

- To do a multibit register, just use multiple D flopss.

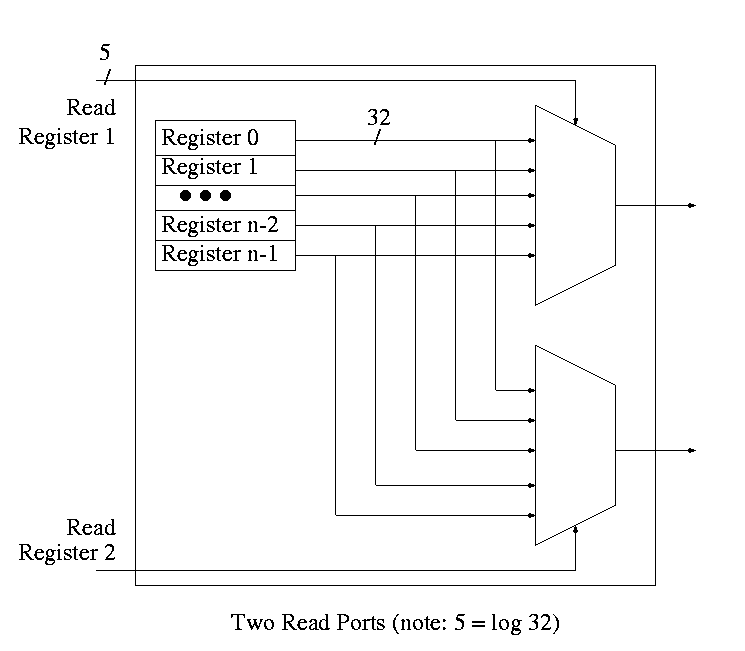

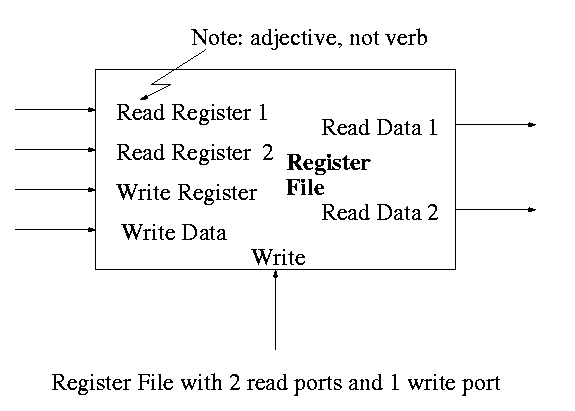

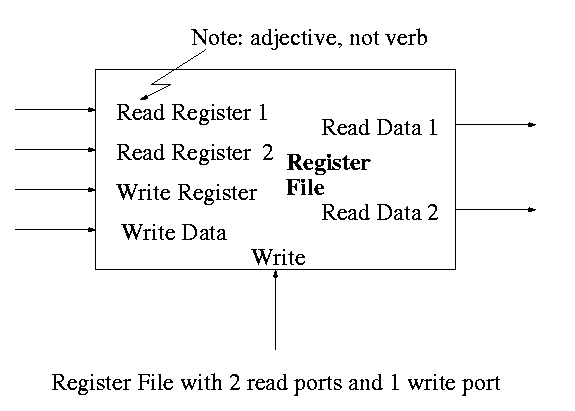

Register File

Set of registers each numbered

- Supply reg#, write line, and data (if a write)

- Can read and write same reg same cycle. You read the old value and

then the written value replaces this old value for subsequent cycles.

- Often have several read and write ports so that several

registers can be read and written during one cycle.

- We will do 2 read ports and one write port since that is

needed for ALU ops. This is Not adequate for superscalar (or

EPIC) or any other system where more than one operation is to be

calculated each cycle.

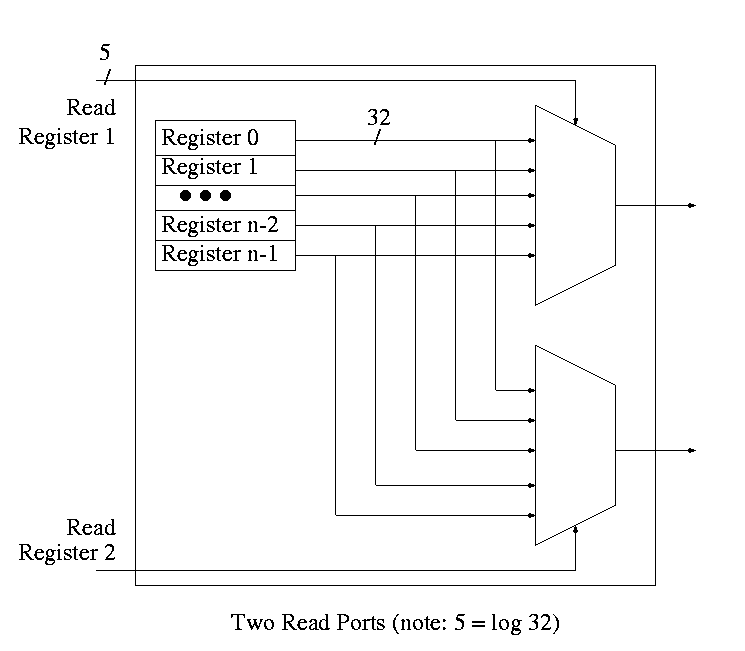

To read just need mux from register file to select correct

register.

- Have one of these for each read port

- Each is an n to 1 mux, b bits wide; where

- n is the number of registers (32 for MIPS)

- b is the width of each register (32 for MIPS)