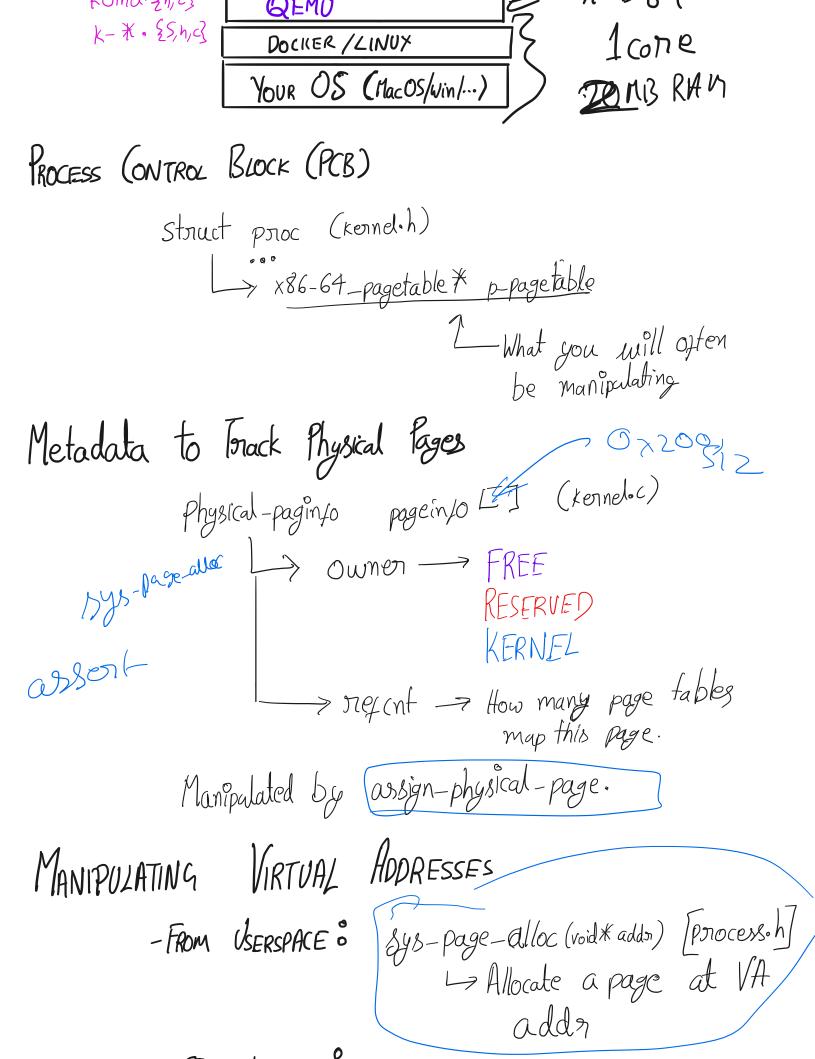

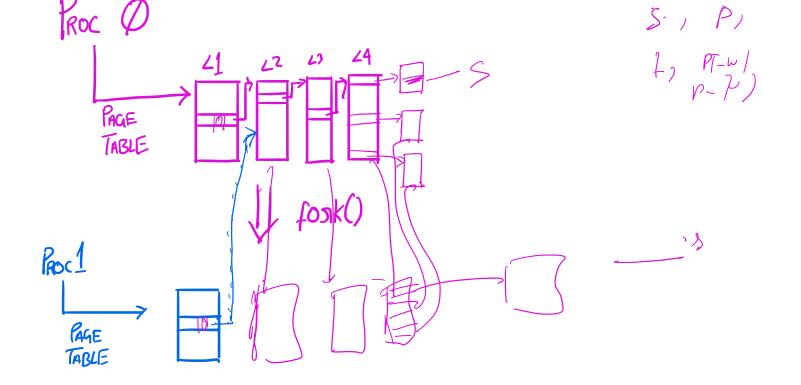

(S202: VIRTUAL MEMORY 3 -LAST CLASS - WALKING THE PAGE TABLES 7 9 9 9 9 0 21 IOX 22 IOX 23 IOX 24 IOX OFF - TLB: TRANSLATION LOOK ASIDE BUFFER L> CACHE PAST TRANSLATION RESULTS -> SAVE TIME ! TODAY - WEENSY OS (LAR4) - PAGE FAULTS & THEIR USES. WEENSY OS - START EARLY = DON'T - REVIEW SESSION: 45 7:15 PM 10/31 - GOAL HERE: PROVIDE SOME CONTEXT. P-allocation.c P-Conk.C P-alloc

Weensy US Kennel

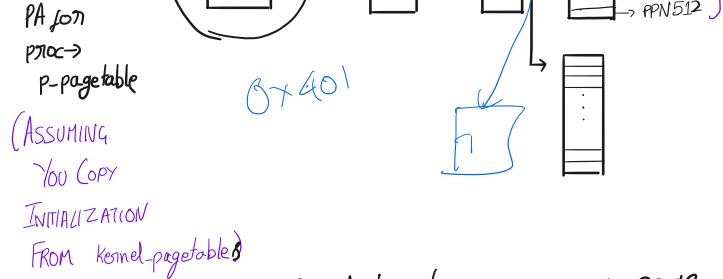

- FROM KERNEL O vintual-memony-map (x86-64... \* page table, Uintptn-t Vallantptn-t part 10000 PAGE ALIGNED Size-t SZ, int perm, 10000 10000 function pointer to allocator) Goals Map Val Va+5Z ASSUMPTION'S CALLER HAS ALREADY CHECKED [Pa ... patsz] CAN BE SAFELY MAPPED. HOW IS THE ALLOCATOR USED? To Mapped for Kennel. % CR3

Q. Want to map a page at vint. address 0x401 000 (vpv 1025)?

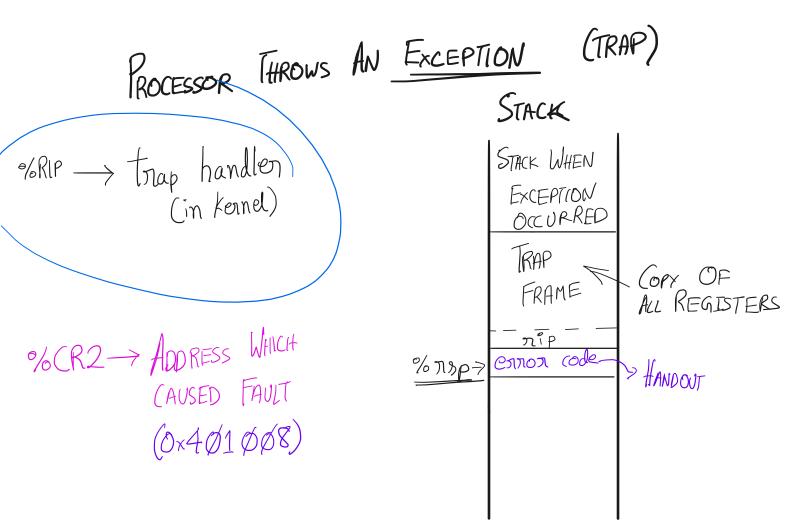

BACK TO PAGE FAULTS

morg 0x 401 008, % Max

NOT PRESENT OR ACCESS NOT ALLOWED

HOW USED

(Next (LASS)

2 COPY ON WRITE.

Mm (proct-nb)

CORE IDEA

-DELAY ACTUALLY COPYING UNTIL NECESSARY

-WHEN NECESSARY?

ON MODIFICATION

3 ACCOUNTING

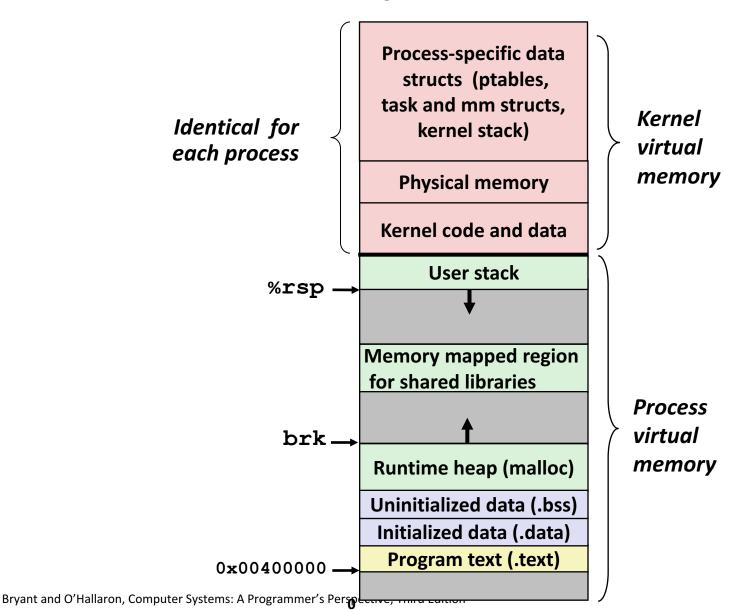

LINUX VA LAYOUT

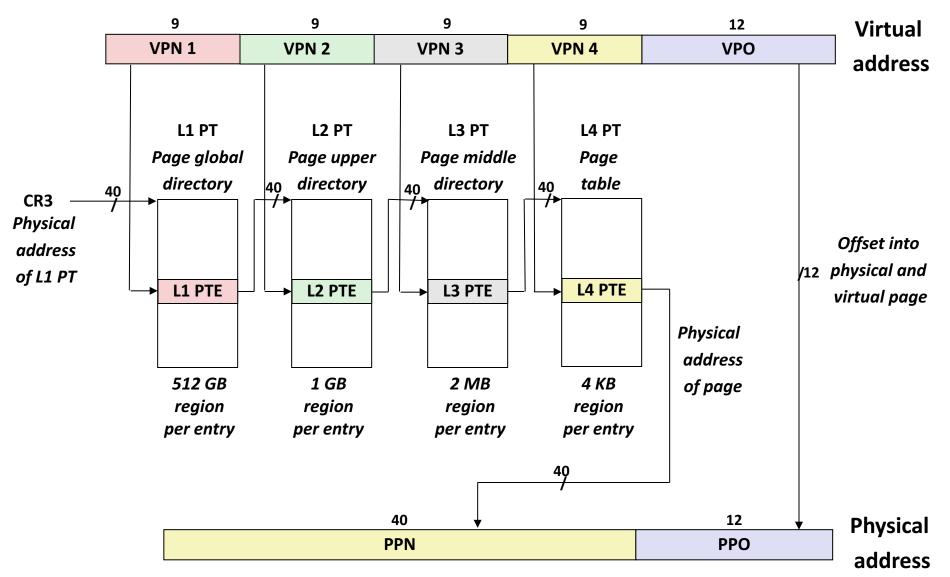

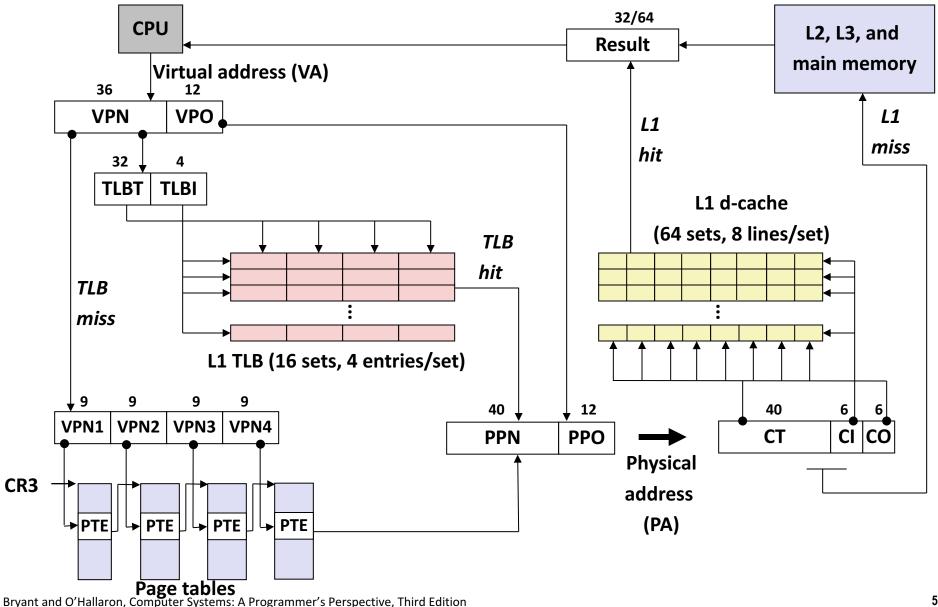

## **Core i7 Page Table Translation**

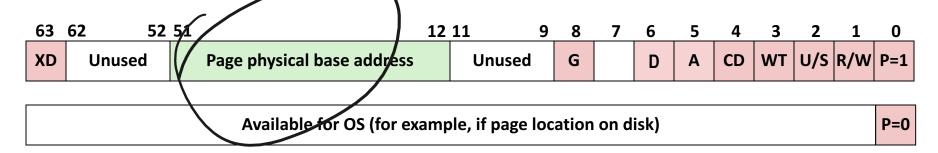

## **Core i7 Level 4 Page Table Entries**

#### Each entry references a 4K child page. Significant fields:

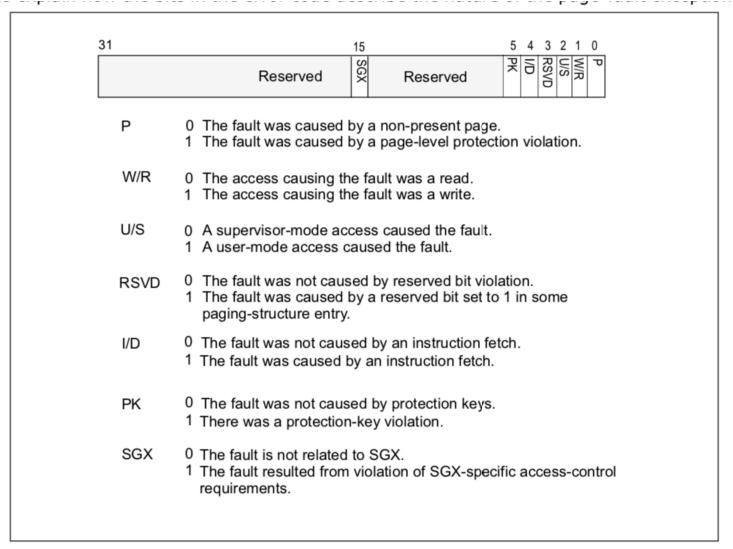

P: Child page is present in memory (1) or not (0)

R/W: Read-only or read-write access permission for this page

**U/S:** User or supervisor mode access

WT: Write-through or write-back cache policy for this page

A: Reference bit (set by MMU on reads and writes, cleared by software)

**D:** Dirty bit (set by MMU on writes, cleared by software)

Page physical base address: 40 most significant bits of physical page address (forces pages to be 4KB aligned)

**XD:** Disable or enable instruction fetches from this page.

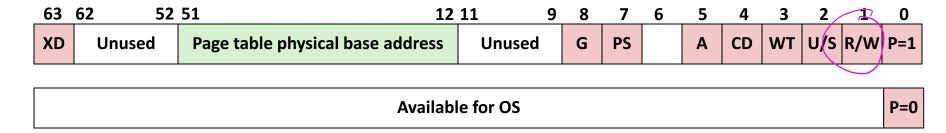

# **Core i7 Level 1-3 Page Table Entries**

#### Each entry references a 4K child page table. Significant fields:

**P:** Child page table present in physical memory (1) or not (0).

**R/W:** Read-only or read-write access access permission for all reachable pages.

**U/S:** user or supervisor (kernel) mode access permission for all reachable pages.

**WT:** Write-through or write-back cache policy for the child page table.

**A:** Reference bit (set by MMU on reads and writes, cleared by software).

**PS:** Page size: if bit set, we have 2 MB or 1 GB pages (bit can be set in Level 2 and 3 PTEs only).

**Page table physical base address:** 40 most significant bits of physical page table address (forces page tables to be 4KB aligned)

**XD:** Disable or enable instruction fetches from all pages reachable from this PTE.

Figure 4-12. Page-Fault Error Code

### **End-to-end Core i7 Address Translation**

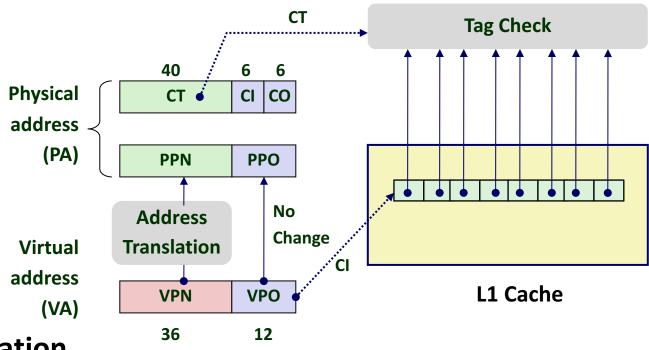

## **Cute Trick for Speeding Up L1 Access**

### Observation

- Bits that determine CI identical in virtual and physical address

- Can index into cache while address translation taking place

- Cache carefully sized to make this possible: 64 sets, 64-byte cache blocks

- Means 6 bits for cache index, 6 for cache offset

- That's 12 bits; matches VPO, PPO  $\rightarrow$  One reason pages are  $2^{12}$  bits = 4 KB

## Virtual Address Space of a Linux Process