11gsiller C

(SWITCH TO SHEET)

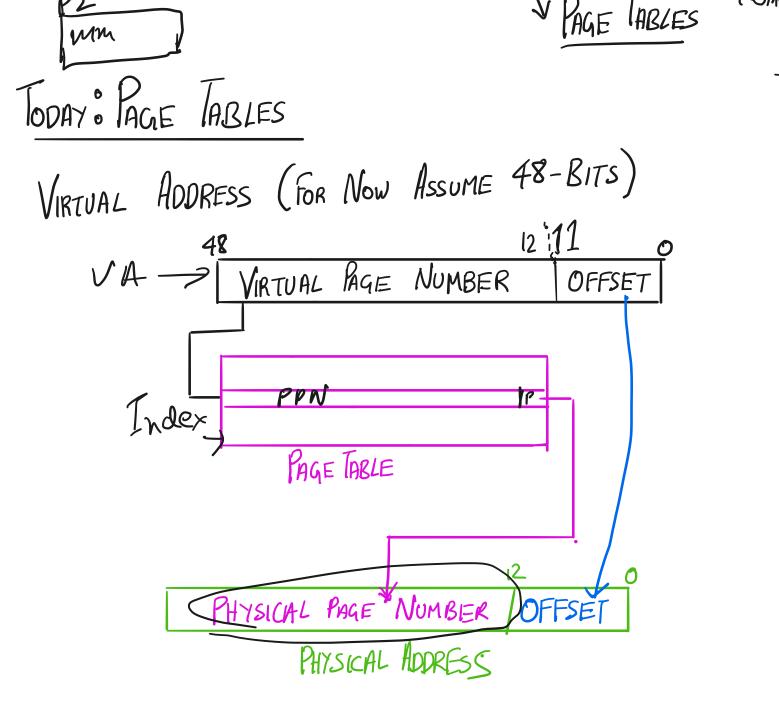

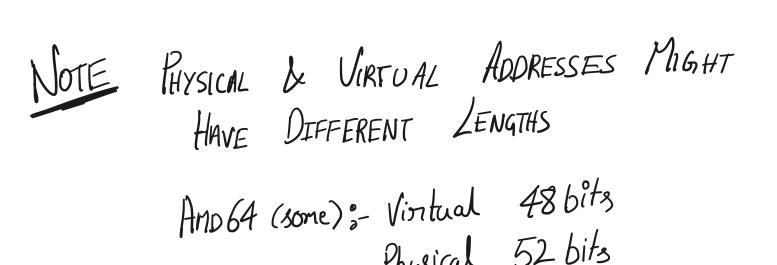

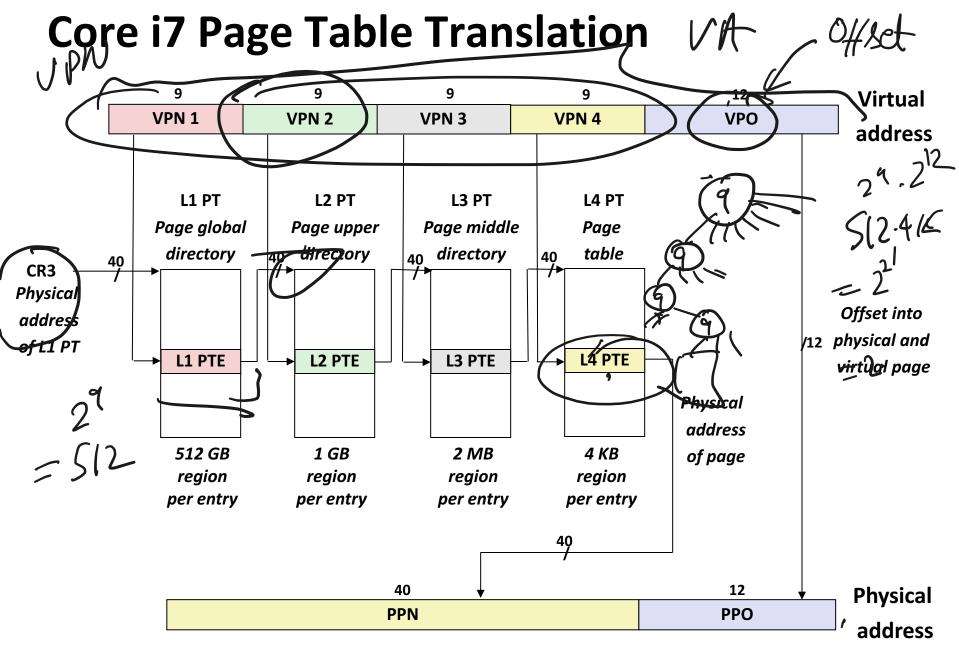

NOTE REMAINING 64-48= 16 bits? All Øon All I LAGE LABLES (ORE PROBLEM ? LOTS OF UNUSED VIRTUAL ADDRESES DON'T WANT TO WASTE SPACE. 36

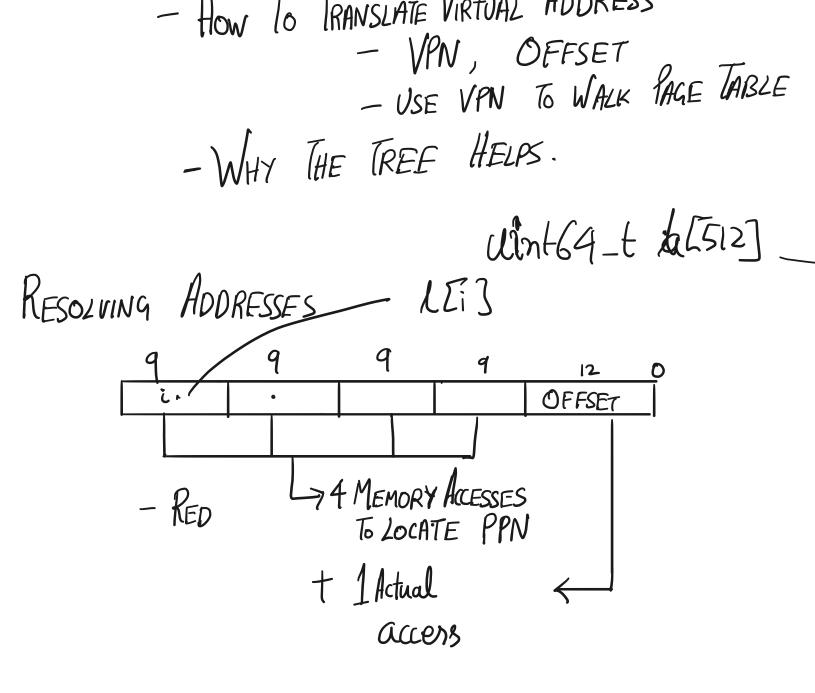

SOLUTION & BUILD A REE

WHAT IS IMPORTANT - FAULTS & NOT PRESENT OR VIOLATE ACCESS CONTROL PERMISSIONS T VILLA MONDECC

- 5x Extra Accesses

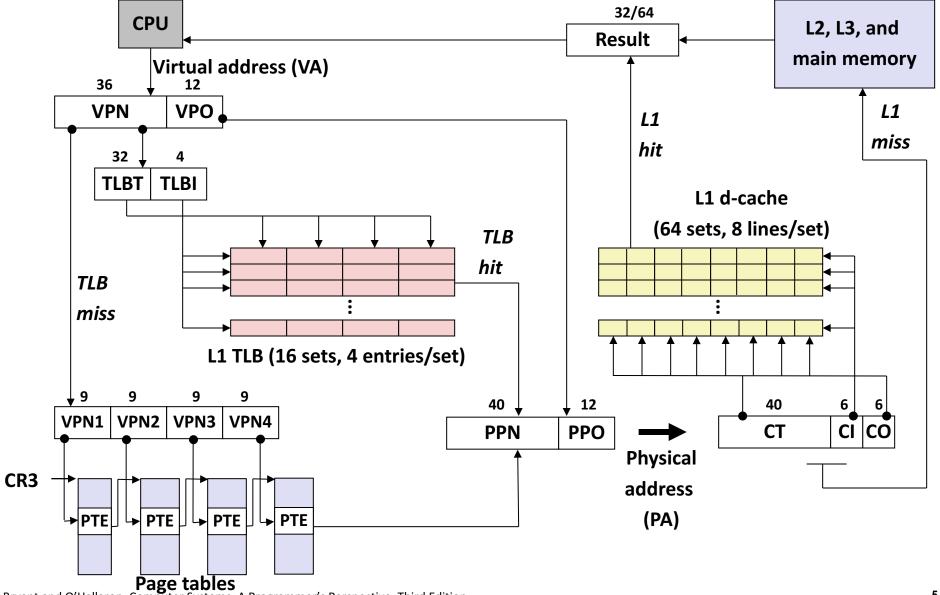

- WANT TO REDUCE OVERHEADS. L-> CACHE RECENT VPN-> PPN

RANSLALION LOOKASIDE TRANSLATIONS BUFFER -> SIZE DICTATED BY HARDWARE USUALLY B/W 64-1024 entries - ON Miss?

72B QUESTION

16 ENTRIES. PROGRAM THAT (AFTER INITIAL START) MISSES TLB ON EACH INSTRUCTION? Q [4096×1] (ODECIME T=0; P'' While (I) rpub(a [i];)

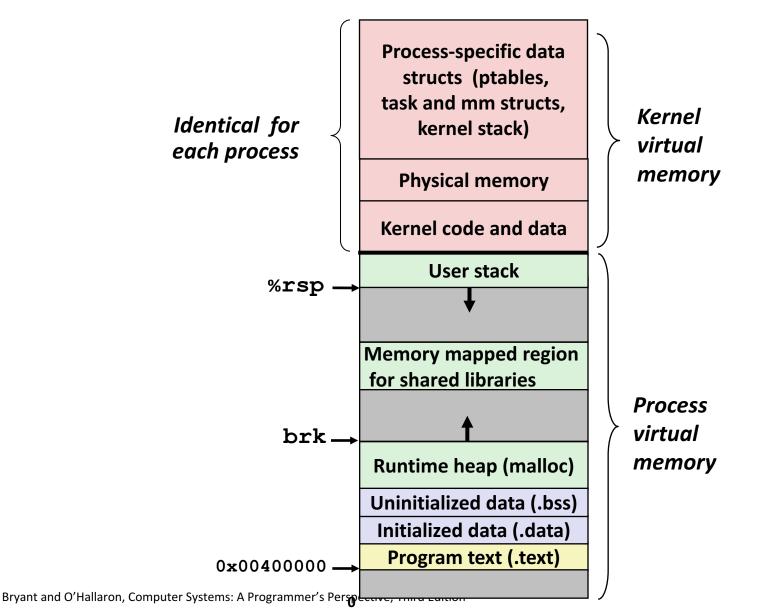

PROCESS MEMORY LAYOUT.

Q096.(7

|                      | 12bils<br>= $2^{12}$<br>= $2^{3} \cdot 2^{10}$<br>= $4\pi$ |

|----------------------|------------------------------------------------------------|

| 2,29 $21P7-7Enbrieg$ |                                                            |

|                      |                                                            |

Bryant and O'Hallaron, Computer Systems: A Programmer's Perspective, Third Edition

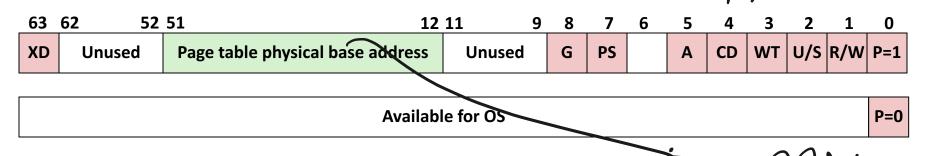

## **Core i7 Level 4 Page Table Entries**

| 63 | 62 52  | 51 1                       | 12 11  | 9 | 8 | 7 | 6 | 5 | 4  | 3  | 2   | 1   | 0   |

|----|--------|----------------------------|--------|---|---|---|---|---|----|----|-----|-----|-----|

| XD | Unused | Page physical base address | Unused |   | G |   | D | Α | CD | WT | U/S | R/W | P=1 |

Available for OS (for example, if page location on disk)

P=0

#### Each entry references a 4K child page. Significant fields:

- P: Child page is present in memory (1) or not (0)

- R/W: Read-only or read-write access permission for this page

- U/S: User or supervisor mode access

- WT: Write-through or write-back cache policy for this page

- A: Reference bit (set by MMU on reads and writes, cleared by software)

- D: Dirty bit (set by MMU on writes, cleared by software)

- Page physical base address: 40 most significant bits of physical page address (forces pages to be 4KB aligned)

- **XD:** Disable or enable instruction fetches from this page.

# Core i7 Level 1-3 Page Table Entries

#### Each entry references a 4K child page table. Significant fields:

- **P:** Child page table present in physical memory (1) or not (0).

- **R/W:** Read-only or read-write access access permission for all reachable pages.

- U/S: user or supervisor (kernel) mode access permission for all reachable pages.

- WT: Write-through or write-back cache policy for the child page table.

- A: Reference bit (set by MMU on reads and writes, cleared by software).

- **PS:** Page size: if bit set, we have 2 MB or 1 GB pages (bit can be set in Level 2 and 3 PTEs only).

- Page table physical base address: 40 most significant bits of physical page table address (forces page tables to be 4KB aligned)

- **XD:** Disable or enable instruction fetches from all pages reachable from this PTE.

| 31   | 15 5 4 3 2 1 0                                                                                                                                                    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Reserved SGX Reserved PR D RSVD P                                                                                                                                 |

| Ρ    | <ul><li>0 The fault was caused by a non-present page.</li><li>1 The fault was caused by a page-level protection violation.</li></ul>                              |

| W/R  | <ul><li>0 The access causing the fault was a read.</li><li>1 The access causing the fault was a write.</li></ul>                                                  |

| U/S  | <ul><li>0 A supervisor-mode access caused the fault.</li><li>1 A user-mode access caused the fault.</li></ul>                                                     |

| RSVD | <ul><li>0 The fault was not caused by reserved bit violation.</li><li>1 The fault was caused by a reserved bit set to 1 in some paging-structure entry.</li></ul> |

| I/D  | <ul><li>0 The fault was not caused by an instruction fetch.</li><li>1 The fault was caused by an instruction fetch.</li></ul>                                     |

| PK   | <ul><li>0 The fault was not caused by protection keys.</li><li>1 There was a protection-key violation.</li></ul>                                                  |

| SGX  | <ul> <li>0 The fault is not related to SGX.</li> <li>1 The fault resulted from violation of SGX-specific access-control requirements.</li> </ul>                  |

#### Figure 4-12. Page-Fault Error Code

## **End-to-end Core i7 Address Translation**

Bryant and O'Hallaron, Computer Systems: A Programmer's Perspective, Third Edition

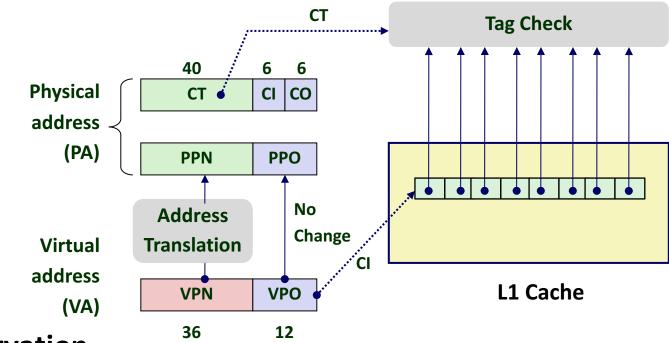

## **Cute Trick for Speeding Up L1 Access**

### Observation

- Bits that determine CI identical in virtual and physical address

- Can index into cache while address translation taking place

- Cache carefully sized to make this possible: 64 sets, 64-byte cache blocks

- Means 6 bits for cache index, 6 for cache offset

- That's 12 bits; matches VPO, PPO  $\rightarrow$  One reason pages are 2<sup>12</sup> bits = 4 KB

### **Virtual Address Space of a Linux Process**

| Q. | PAGES REQUIRED TO ALLOCATE                                              |

|----|-------------------------------------------------------------------------|

|    | - 1 Byte                                                                |

|    | $-4$ KB (PAGE SIZE) = $2^{12}$ BYTES                                    |

|    | $-512.4$ KB $\equiv 2^{9}.2^{12}$ BYTES $\equiv 2MB$                    |

|    |                                                                         |

|    | $-512 \cdot 2MB \equiv 1GB \equiv 2^{9} \cdot 2^{9} \cdot 2^{12} BYTES$ |

|    | <ul> <li></li></ul>                                                     |

|    |                                                                         |

|    |                                                                         |

|    |                                                                         |

|    |                                                                         |

|    | • • • • • • • • • • • • • • • • • • •                                   |

|    | • • • • • • • • • • • • • • • • • • •                                   |

|    | • • • • • • • • • • • • • • • • • • •                                   |