# MECHANISMS TO ADVANCE THE ADOPTION OF PROGRAMMABLE HIGH-SPEED PACKET-PROCESSING PIPELINES

by

## Tao Wang

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Department of Computer Science

New York University

May, 2025

| Dr. Anirudh Sivaraman |

|-----------------------|

| Dr. Aurojit Panda     |

#### © Tao Wang

All rights reserved, 2025

# **D**EDICATION

To all the ones who helped me survive.

## ACKNOWLEDGEMENTS

When I reflect on my past six-year journey toward a Ph.D., I realize that the most valuable asset I have is not the challenging projects I have done but the precious friendships with so many individuals along the journey. It would not have been possible without the support, guidance, and encouragement of them, to whom I am deeply grateful.

First and foremost, I would like to express my sincere gratitude to my advisors for their invaluable guidance, patience, and unwavering support during my journey.

Aurojit Panda: As an advisor, he is omniscient (I will not question that) about everything. His hands-on experience in building and optimizing systems always guides us in the right direction through the challenges. As a friend, you can easily feel how energetic he is about the research projects. I still remember he was introducing his friends to me and raising a thumbs-up high in the crowd after my presentation of Menshen at NSDI'22, which really gave me a sense that you are not alone in this challenging and exhausting journey. Furthermore, life is not a place full of candy, Panda always gives different perspectives to help you see through murky things. If possible, I would consult him for advice throughout my life.

Anirudh Sivaraman: Anirudh, as my advisor has deeply shaped my research taste during my early years at NYU. I still remember he told me that we should be careful about picking the topics we really want to work on, since we only have limited time (well, maybe I understood it in a wrong way that I so many times directly rejected the early ideas—which were shown to be worth doing by other groups—proposed by him). More importantly to me, a usually pessimistic guy from Wuhan,

Anirudh had done so many mental massages during the pandemic, which gave me a lot of relief. I would say a sincere thank you (in the form of a message rather than a direct phone call, which really drove me nervous in my early years).

*Gianni Antichi:* As the Chinese proverb says, an elderly person in the family is like a treasure. Gianni is such an "elderly" person during my journey. He is always ready and willing to help even for the tiny bugs of handshaking in Verilog. His experience in FPGA development helped me a lot when we started both Menshen and QingNiao projects. Most importantly, I can sense the energy and enthusiasm about the research itself when working with him. If allowed, I would someday join his paper reading group at a random bar drinking beers with him and Panda:-).

I am also deeply thankful to my other dissertation committee members Jinyang Li and Ratul Mahajan for their time, thoughtful critiques, and constructive feedback, which have greatly improved the quality of my dissertation.

Another heartfelt thank you goes to my friends who I had collaborated with closely.

**Fabian Ruffy:** During the collaboration with him on the Gauntlet project, I found Fabian is phenomenally hard-working and skilled at team management. But most importantly, he aims super high for all his projects, deciding to build practical tools that can be used by the broader developers. All his attitudes influenced a lot me in my own projects.

*Xiangrui Yang:* Xiangrui is literally the first guy who taught me how to program in Verilog for a big project. I still remember the days and nights that I worked before the computer waiting for the synthesis results and kept improving my implementation with him. Interestingly, this experience gives me a chance to practice the Pomodoro technique of time management.

Jinkun Lin: Jinkun is an optimistic guy who helped me survive the "potential" mental breakdown when we were doing the "bumpy" QingNiao project. We took a holistic approach which involves modifying everything from the application to the hardware in QingNiao, which is challenging and daunting in terms of the engineering effort. I still remember Jinkun's warm words and optimistic attitudes along the journey we developed QingNiao.

*Hang Zhu:* Hang is an insightful researcher in the networking field. It was an interesting opportunity for me to collaborate with Hang, since we have similar visions but different angles to tackle the problem of how to support multitenancy for programmable networks. The collaboration with Hang taught me that we should not always consider things from one specific angle. The software world is also amazing.

Alex Forencich: Alex, an unselfish researcher from UCSD, has maintained the repository of Corundum, which I have used throughout my research. He has devoted himself to the open-source community of FPGA development and taught me how important it is to be enthusiastic about the things you are doing, especially in the field of developing hardware. To make the prototype on FPGA happen needs consistent effort on improving the every low-level details of your implementations.

I would also like to acknowledge all the support from my friends and colleagues in NYU NetSys group including Cheng Tan, Lingfan Yu, Changgeng Zhao, Yu Cao, Xiangyu Gao, Anqi Zhang, Jiaxin Lin, Qiongwen Xu, Zhanghan Wang and many others.

Last, but not least, I probably would not have gone this far without the tremendous support from my parents. Although I always have different or even opposite perspectives with them, they always support my decisions and hope the best for me in the end without hesitation.

## ABSTRACT

Modern high-speed programmable packet-processing pipelines—typically built on the Reconfigurable Match Table (RMT) architecture—have enabled a wide range of network offloads, such as in-network telemetry, caching, and machine learning parameter aggregation. However, these capabilities remain largely inaccessible to a broader range of users and applications.

This dissertation investigates the barriers to broader adoption from two key perspectives: multitenancy and general application-level, *i.e.*, Layer 7 (L7), processing. It argues that expanding adoption requires new hardware primitives alongside complementary software toolchains. To address these challenges, the dissertation introduces two systems: (1) Menshen, which provides isolation mechanisms that allow multiple programs to safely share a single pipeline without interfering with each other; and (2) QingNiao, a system designed for L7 dispatch—a pervasive and crucial L7 processing in network infrastructure—offering a holistic solution that combines novel hardware architecture design with a high-level programming model to enable efficient L7 dispatch on programmable pipelines.

# **C**ONTENTS

| De | edicat  | ion                                          | iii |

|----|---------|----------------------------------------------|-----|

| Ac | know    | rledgments                                   | iv  |

| Al | ostrac  | et                                           | vii |

| Li | st of l | Figures                                      | xi  |

| Li | st of T | Tables                                       | xiv |

| 1  | Intr    | oduction                                     | 2   |

| 2  | Back    | kground                                      | 5   |

|    | 2.1     | Reconfigurable Match Table                   | 5   |

|    | 2.2     | RMT's Limitations for Multitenancy           | 7   |

|    | 2.3     | RMT's Limitations for General L7 Processing  | 9   |

| 3  | Men     | nshen                                        | 11  |

|    | 3.1     | Requirements for Isolation Mechanisms on RMT | 11  |

|    | 3.2     | Menshen's Approach                           | 13  |

|    | 3.3     | Menshen's Design                             | 14  |

|    |         | 3.3.1 Menshen Software                       | 15  |

|   |      | 3.3.2 Menshen Hardware                    | 18 |

|---|------|-------------------------------------------|----|

|   |      | 3.3.3 Optimizations for Menshen Hardware  | 24 |

|   | 3.4  | Implementation                            | 26 |

|   |      | 3.4.1 Menshen Software                    | 26 |

|   |      | 3.4.2 Menshen Hardware                    | 26 |

|   |      | 3.4.3 Corundum and NetFPGA Integrations   | 30 |

|   | 3.5  | Evaluation                                | 32 |

|   |      | 3.5.1 Does Menshen meet its requirements? | 33 |

|   |      | 3.5.2 Menshen Performance                 | 37 |

|   | 3.6  | Related Work                              | 40 |

|   | 3.7  | Summary                                   | 42 |

| 4 | Qing | Niao 4                                    | 43 |

|   | 4.1  | The case for L7 dispatch in hardware      | 43 |

|   | 4.2  | Challenges to offloading L7 dispatch      | 46 |

|   | 4.3  | QingNiao Design                           | 47 |

|   | 4.4  | An Example of QingNiao                    | 48 |

|   |      | 4.4.1 QingNiao Software Stack             | 50 |

|   |      | 4.4.2 QingNiao Hardware Architecture      | 52 |

|   | 4.5  | QingNiao Implementation                   | 56 |

|   |      | 4.5.1 QingNiao Hardware Prototype         | 56 |

|   |      | 4.5.2 QingNiao Software Prototype         | 59 |

|   |      | 4.5.3 Optimizations of QingNiao           | 61 |

|   | 4.6  | Evaluation                                | 61 |

|   |      | 4.6.1 Integration with RocksDB            | 65 |

|   |      | 4.6.2 Microbenchmarks                     | 67 |

| Bi | bliogi | raphy                      | 80 |

|----|--------|----------------------------|----|

|    | 5.1    | Limitation and Future work | 78 |

| 5  | Con    | clusion                    | 77 |

|    | 4.8    | Summary                    | 75 |

|    | 4.7    | Related Work               | 73 |

# List of Figures

| 2.1  | Example of an RMT pipeline                                                           | 6  |

|------|--------------------------------------------------------------------------------------|----|

| 2.2  | Example of a parser graph. The nodes represent the parsing states, while the arrows  |    |

|      | represent the transitions between parsing states                                     | 6  |

| 3.1  | An example of running multiple programs on a single RMT pipeline. We show the        |    |

|      | resources allocated to different programs by shading them in the appropriate colors. | 11 |

| 3.2  | Overview of Menshen's software toolchains and hardware primitives                    | 15 |

| 3.3  | Menshen builds atop an RMT [73] pipeline. Specifically, Menshen introduces           |    |

|      | Yellow components and modifies Green ones                                            | 18 |

| 3.4  | Menshen programmable parser                                                          | 19 |

| 3.5  | Menshen processing stage                                                             | 20 |

| 3.6  | Three optimization techniques applied in Menshen. Numbered circles refer to          |    |

|      | specific techniques detailed in §3.3.3                                               | 24 |

| 3.7  | Formats of Menshen's packets and tables                                              | 27 |

| 3.8  | Testbed setup. Red arrow shows packet flow                                           | 32 |

| 3.9  | Compilation time of Menshen.                                                         | 34 |

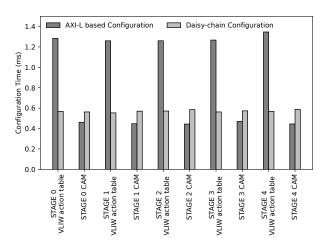

| 3.10 | Configuration time of Menshen.                                                       | 34 |

| 3.11 | Configuration time comparison for AXI-L based (estimated) and Menshen's daisy-       |    |

|      | chain configuration (measured)                                                       | 35 |

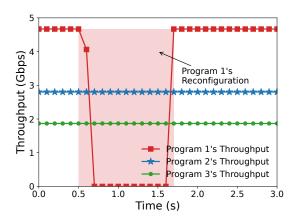

| 3.12 | Disruption-free reconfiguration measured every 0.1 s                             | 36 |

|------|----------------------------------------------------------------------------------|----|

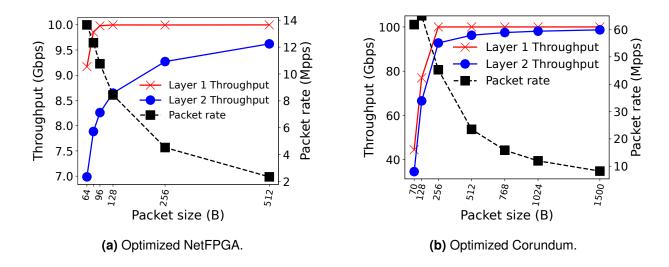

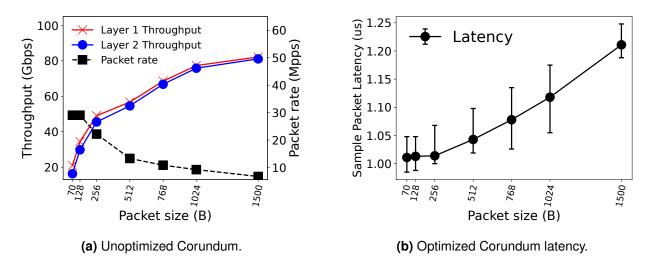

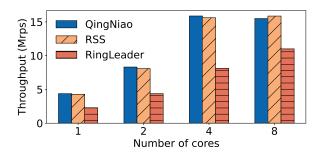

| 3.14 | Results for performance benchmarks                                               | 38 |

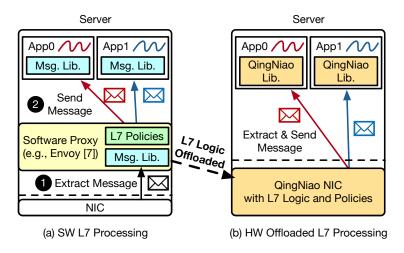

| 4.1  | Architectural comparison of L7 processing implemented in software and hardware   |    |

|      | (e.g., our solution QingNiao)                                                    | 44 |

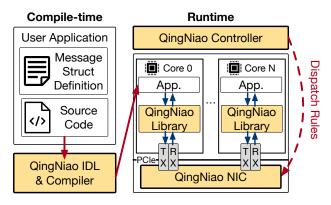

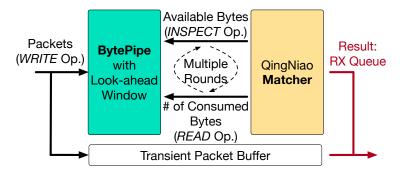

| 4.2  | QingNiao's design consists of the colored components                             | 47 |

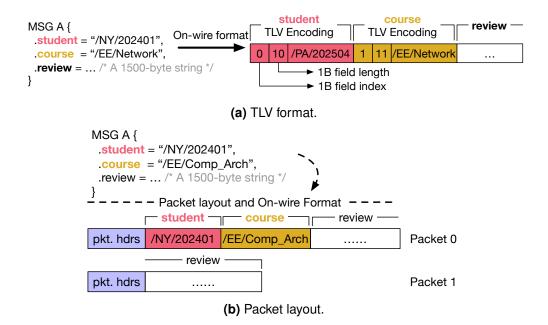

| 4.3  | Example of the message struct definition and dispatch rules                      | 49 |

| 4.4  | Example of QingNiao on-wire format for a message struct with two fields, where   |    |

|      | fields 'student' and 'course' are used for dispatch.                             | 51 |

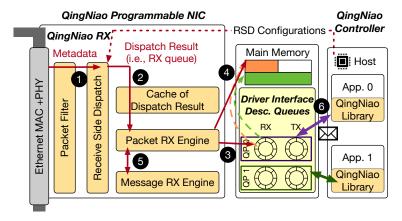

| 4.5  | QingNiao's RX data path overview.                                                | 51 |

| 4.6  | Receive Side Dispatch's components: (1) BytePipe with look-ahead window; (2)     |    |

|      | programmable Matcher which implements skip-and-match.                            | 55 |

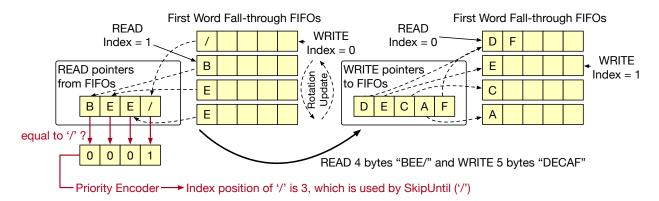

| 4.7  | A BytePipe example with read and write index being 1 and 0 at the beginning,     |    |

|      | respectively. A read operation reads out 4 bytes (i.e., "BEE/") and a following  |    |

|      | write operation writes in 5 bytes (i.e., "DECAF"). BytePipe leverages a priority |    |

|      | encoder to indicate the position of the specified character used by SkipUntil    | 56 |

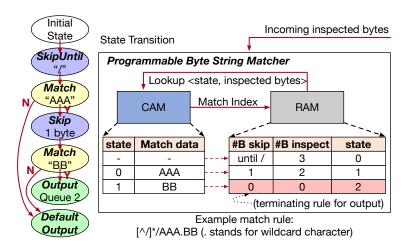

| 4.8  | Matcher implements the skip-and-match. Skip and Match are encoded in RAM         |    |

|      | and CAM entries respectively. RAM entries with skipping and matching 0 bytes     |    |

|      | denote exit states: it shows the output queue index in the last column           | 57 |

| 4.9  | QNP packet header definition                                                     | 59 |

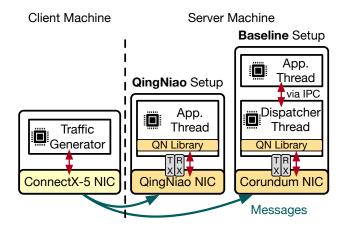

| 4.10 | Experimental setup                                                               | 62 |

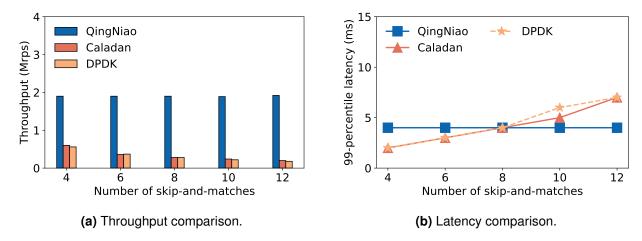

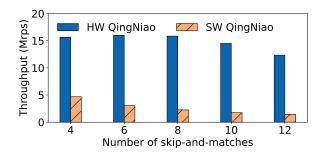

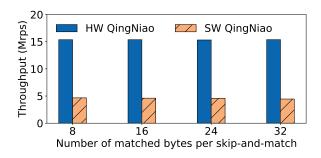

| 4.11 | On throughput, QingNiao outperforms Caladan by 6.54× averagely with varying      |    |

|      | the number of skip-and-matches.                                                  | 64 |

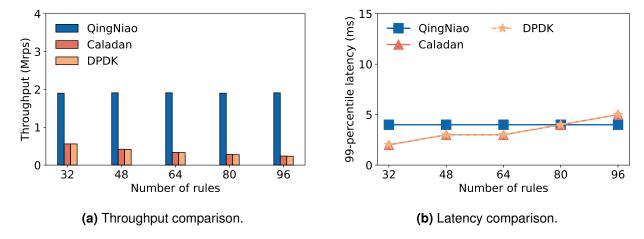

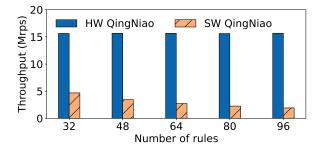

| 4.12 | On throughput, QingNiao outperforms Caladan by 5.67× averagely with varying      |    |

|      | the number of rules dimension.                                                   | 65 |

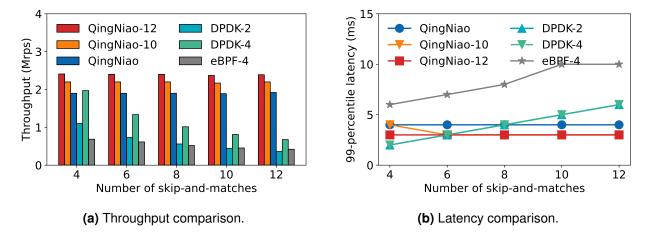

| 4.13 | With the same number of cores, QingNiao outperforms software by 3.91× averagely  |    |

|------|----------------------------------------------------------------------------------|----|

|      | with varying the number of skip-and-matches on throughput                        | 65 |

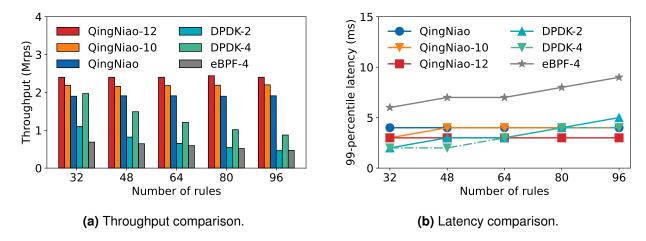

| 4.14 | With the same number of cores, QingNiao outperforms software by 3.34× averagely  |    |

|      | with varying the number of rules dimension on throughput                         | 66 |

| 4.15 | QingNiao achieves comparable performance as hardware L3/4 dispatcher             | 69 |

| 4.16 | QingNiao outperforms software implementation by 6.49× averagely with varying     |    |

|      | number of skip-and-matchs.                                                       | 69 |

| 4.17 | QingNiao outperforms software implementation by 5.74× averagely with varying     |    |

|      | number of rules                                                                  | 69 |

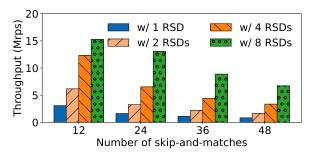

| 4.18 | Having parallel RSDs improves throughput                                         | 69 |

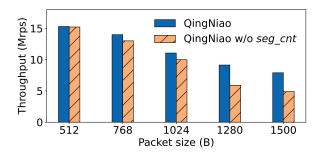

| 4.19 | Introducing seg_cnt improves throughput                                          | 70 |

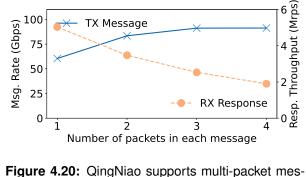

| 4.20 | QingNiao supports multi-packet messages                                          | 70 |

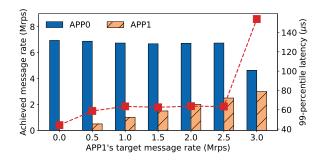

| 4.21 | APP0's throughput decreases and latency increases as APP1's rate increases       | 70 |

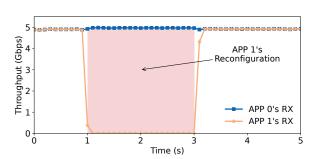

| 4.22 | APP0's rate is not impacted when APP1 is reconfiguring in QingNiao at runtime    | 70 |

| 4.23 | QingNiao outperforms its software implementation by 3.36× averagely with varying |    |

|      | number of matched bytes                                                          | 73 |

# LIST OF TABLES

| 3.1 | Summary of Menshen's mechanisms.                                                  | 14 |

|-----|-----------------------------------------------------------------------------------|----|

| 3.2 | Supported operations in Menshen's ALU                                             | 30 |

| 3.3 | Hardware resources in Menshen                                                     | 31 |

| 3.4 | Evaluated use cases                                                               | 32 |

| 3.5 | Resources used by 5-stage Menshen pipeline, on NetFPGA SUME and AU250             |    |

|     | boards, compared with reference switch, Corundum NIC, and RMT                     | 37 |

| 4.1 | Dissection of additional latency brought by Envoy.                                | 45 |

| 4.2 | QingNiao's latency reported in simulation and testbed. QingNiao adds 6 cycles per |    |

|     | skip-and-match (S&M)                                                              | 68 |

| 4.3 | FPGA resources usage for module of parallel RSDs                                  | 70 |

| 4.4 | FPGA resource usage of QingNiao vs Corundum                                       | 72 |

## Previously Published Materials

Chapter 3 combines materials from two previous publications [135, 136]:

- Tao Wang\*, Hang Zhu\*, Fabian Ruffy, Xin Jin, Anirudh Sivaraman, Dan Ports, and Aurojit Panda. Multitenancy for Fast and Programmable Networks in the Cloud. In USENIX HotCloud, 2020. (\*Co-primary authors)

- Tao Wang, Xiangrui Yang, Gianni Antichi, Anirudh Sivaraman, and Aurojit Panda. Isolation

Mechanisms for High-speed Packet-processing Pipelines. In USENIX NSDI, 2022.

Chapter 4 adapts materials from the following arXiv paper [134]:

Tao Wang, Jinkun Lin, Gianni Antichi, Aurojit Panda, and Anirudh Sivaraman. Application-Defined Receive Side Dispatching on the NIC. In arXiv, 2024.

## 1 | Introduction

Programmable high-speed packet-processing pipelines—usually integrated in networking devices like switches/routers [22] and Smart Network Interface Cards (SmartNICs [35, 2])—allow the data center network infrastructure to provide additional features beyond packet forwarding/routing. Recent work has demonstrated that offloading functionalities such as in-network caching [100], consensus protocols [99, 107], congestion control based on in-network telemetry [108], monitoring [71], etc., to these programmable networking devices can improve throughput and reduce latency, thus freeing up precious CPU cycles [82].

However, the benefits of these programmable networking devices<sup>1</sup> are not yet broadly accessible to a wider range of users and applications.

One major barrier is **multitenancy**: the ability for **multiple** independently developed network offloads to simultaneously run atop a **single** programmable high-speed packet-processing pipeline without interfering with each other.

Most existing systems assume that a single offload occupies the entire programmable pipeline in a fully dedicated setting. However, as network programmability matures, there is growing demand for devices that can multiplex offloads to conserve hardware resources. For example, public cloud may allow tenants to install their own offloads (*e.g.*, in-network caching [100], telemetry [71]) on the cloud provider's devices. Similarly, within a single organization, multiple teams may need

<sup>&</sup>lt;sup>1</sup>Throughout this dissertation, we focus our discussion on Application-Specific Integrated Circuit (ASIC) based high-speed packet-processing pipelines that are typically built on a Reconfigurable Match Table (RMT) architecture, as detailed in Chapter 2.

to colocate different offloads, e.g., an in-network measurement, and an in-network aggregation module for machine-learning [126].

Another barrier is support for general application-level, *i.e.*, Layer 7 (L7), processing. Most existing systems' offloads only work on per-packet network headers (*e.g.*, TCP/IP [47]), which have fixed-length fields. However, L7 messages can be highly variable as application developers can define their own messages [23, 43]. For instance, a web server may first extract the path field from the HTTP header [46] and then respond with appropriate contents. The path field can vary in length, and sometimes extends to tens of bytes exceeding the parsing capacity of the current programmable pipelines as detailed in §2.

Unfortunately, today's ASIC-based high-speed programmable packet-processing pipelines—commonly built on the Reconfigurable Match Table (RMT) [73] architecture, as seen in commercial products like Tofino [22] switch, Intel Mount Evans IPU [21], Pensando SmartNIC [2]—do not adequately support the following:

- **Multitenancy.** They lack the isolation mechanisms to simultaneously run multiple offloads safely without interfering with each other, like accessing allocated hardware resources or achieving non-degrading performance.

- **General L7 processing.** They cannot parse or act on variable-length L7 fields located at arbitrary offsets in packet payloads, making it infeasible to offload application-level functionalities that operate on such variable-length L7 fields.

In this dissertation, we present the design and implementation of two systems, *i.e.*, Menshen and QingNiao, to augment existing programmable pipelines with the support of multitenancy and L7 processing, respectively. Our systems are based on the observation that:

**Thesis Statement.** To enable broader adoption of the programmable pipelines among application developers—particularly in shared environments like public clouds—mechanisms that combine new hardware primitives with supporting software toolchains are essential. These mechanisms

nisms must make programmable pipelines more accessible and provide application-defined offloads with strong performance improvements and isolation guarantees.

The remainder of this dissertation is organized as follows: We provide the background information in Chapter 2 and focus on the discussion of the barriers hindering existing programmable pipelines from being widely adopted. Then in Chapter 3, we present Menshen, a system that provides isolation mechanisms for running multiple offloads on a single programmable pipeline. Next in Chapter 4, we present QingNiao, a framework for the developers to harvest the benefits of the programmable pipeline by specifically enabling offloading the functionality of L7 dispatch. Finally, we conclude by describing limitations and future work in Chapter 5.

## 2 | Background

We begin by introducing the detailed architecture of the ASIC-based high-speed packet-processing pipeline, *i.e.*, Reconfigurable Match Table [73] (RMT) architecture which is widely recognized in both academia (*e.g.*, research prototypes [100, 99, 107] are built atop, etc.) and industry (*e.g.*, commercial products, like Intel Tofino switches [22] and Pensando SmartNICs [2], are released). We then elaborate on the reasons why such RMT-based packet-processing pipelines are incapable of supporting multitenancy and general L7 processing.

#### 2.1 Reconfigurable Match Table

Programmable networking devices fall into three main categories: (1) Application-Specific Integrated Circuit (ASIC) based high-speed packet-processing pipelines *e.g.*, Intel Tofino switch [22], Pensando SmartNIC [2]; (2) Field Programmable Gate Arrays (FPGA) based devices like Cisco Nexus SmartNIC [8]; (3) Multicore System on a Chip (SoC) based devices like Marvell LiquidIO SmartNIC [28]. Each offers a different tradeoff between performance (*e.g.*, device throughput, clock speed, power consumption, etc.) and flexibility (*e.g.*, programmability). Among these, ASIC-based devices provide the highest performance potential compared to the other two [82], which is crucial as networks scale to 400Gbps and beyond. Thus, in this dissertation, we focus on ASIC-based high-speed packet-processing pipelines using the RMT architecture [73] hereafter.

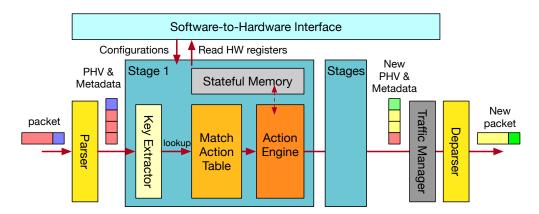

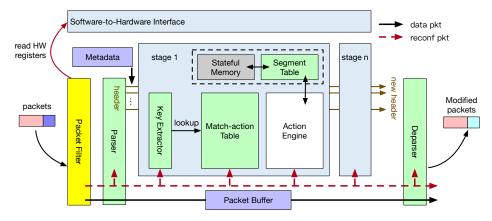

Architectural overview. As depicted in Figure 2.1, an RMT pipeline typically comprises a pro-

Figure 2.1: Example of an RMT pipeline.

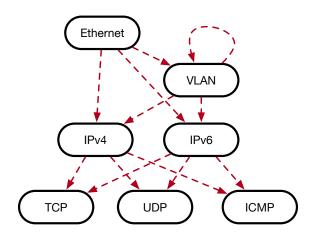

**Figure 2.2:** Example of a parser graph. The nodes represent the parsing states, while the arrows represent the transitions between parsing states.

grammable parser, multiple stages, a traffic manager, and a final programmable deparser at the end. Except for the traffic manager—which is used for packet scheduling—, other elements are programmable and exposed to the developer: typically, a compiler [39] is used to convert the application offload/program<sup>1</sup> into the configurations, which are installed on the pipeline via a software-to-hardware interface.

**Programmable parser.** At a high level, the parser of each offload is represented by a parser graph shown in Figure 2.2. When a packet comes in, the parser will serially traverse through the packet's byte stream according to the parser graph to match the nodes/states configured, and extract the

<sup>&</sup>lt;sup>1</sup>We use offload and program interchangeably in this dissertation. Both terms represent the parts of an application that the developer intends to offload to the hardware.

related header fields. For example, as Figure 2.2 shows, the parser graph will first check whether it is an Ethernet packet and then move along the edges/transitions to reach the final nodes/states to see whether the packet is a TCP, UDP, or ICMP packet. In this way, the parser extracts the header fields (*e.g.*, IP source and destination addresses, etc.)—usually program-specific—from the packet and stores them in the Packet Header Vectors (PHVs). Along with the pipeline metadata (*e.g.*, the port where the packet is received, etc.), PHVs are passed to the following consecutive stages. Such a programmable parser is usually implemented using a Ternary Content Addressable Memory (TCAM) and a Static Random Access Memory (SRAM) as discussed in [89].

Programmable stages. Each stage forms keys out of headers, looks up the keys in a match-action table, and then performs the matched actions. Specifically, within a stage, upon receiving PHVs with the metadata, a key extractor is configured in a per-program manner to combine fields from the PHVs and the metadata to generate the key. Then, this key is compared against the entries in the match-action table for the associated action, which is carried out in the action engine, and the results are written back to the PHVs and passed to the next stage. For a concrete example, to fulfill the functionality of a Network Address Translator (NAT), both the packet's IP source and destination addresses are kept in the PHVs. A stage is configured to match against the incoming packet's IP source address and modify its destination IP address accordingly based on the address translation table configured.

**Programmable deparser.** After all processing stages, deparser assembles the modified PHVs back to the packet according to the parser graph configured, which is the reverse path of the parser, and emits the packet out from the pipeline.

## 2.2 RMT's Limitations for Multitenancy

As described, RMT allows compiling offloads into pipeline configurations that can be directly loaded into the pipeline. It does not natively support running multiple independently developed

offloads on a single pipeline. There are several key limitations:

- It lacks the interface to coordinate different offloads. For example, two configurations of two application offloads might conflict with each other after compilation (e.g., without coordination, they might be both packed into the same stage without enough resources), which forbids them from being successfully loaded on the same device.

- It lacks the interface to specify the hardware resources used by each offload. Although some annotations [39] are provided to indicate how to place offloads, it is challenging to fine-tune those annotations since they are too coarse-grained and may not be strictly enforced.

- It lacks the support of disruption-free reconfigurations. Suppose one developer wants to add features to its offload, it should be guaranteed that its reconfigurations do not impact the running offloads. However, existing RMT can not support disruption-free reconfiguration since it has to refresh the whole pipeline.

Inherently, the RMT architecture poses unique challenges for isolation because its pipeline design means that neither an OS nor a hypervisor can be used to enforce isolation in the data plane.<sup>2</sup> This is because RMT is a *dataflow* or spatial hardware architecture [68, 78] with a set of instructions units continuously processing data (packets). This is in contrast to the Von Neumann architecture found on processors [59], where a program counter decides what instruction to execute next. As such, an RMT pipeline is closer in its hardware architecture to an FPGA or a CGRA [118] than a processor. This difference in architecture has important implications for isolation. The Von Neumann architecture supports a *time-sharing* approach to isolation (in the form of an OS/hypervisor) that runs different programs on the CPU successively by changing the program counter to point to the next instruction of the next module, which can not be directly applied to the *dataflow* architecture like RMT.

<sup>&</sup>lt;sup>2</sup>An OS does run on the network device's control CPU, allowing isolation in the control plane. Our focus is the isolation of the RMT pipeline itself.

To this end, in Chapter 3, we first lay out the requirements of multitenancy for RMT pipelines. Then, we propose a software-hardware codesign, called Menshen, which leverages *space-partitioning* to fulfill the desired requirements.

## 2.3 RMT's Limitations for General L7 Processing

Additionally, as discussed, RMT is inherently constrained by its design and its hardware resources, which limits its capability of processing general L7 fields. The philosophy of RMT is to (1) extract, (2) store, and (3) modify the related fields by using the PHVs, which means that:

- Parsing complexity. RMT is not able to host an offload if its parser graph is too complex to be loaded onto the pipeline.

- **PHV limitation.** RMT can not store the fields to the PHVs if the lengths of the fields used in the offload are excessively long.

- **Action limitation.** RMT can not provide the desired modifications to the fields if the operations—beyond addition, subtraction, etc.[135]—are too complicated.

However, this is always the case for the general L7 processing. Taking HTTP load balancer [34] as an example, it usually operates on the path field inside the HTTP header. The path field usually encapsulates the URLs that have variable lengths and start at arbitrary offsets of a packet. This makes it hard for RMT to process.

First, different from extracting header fields for L3/4 fields where the length is fixed, in order to extract the URLs, the developer can not specify the fixed size of such fields. Instead, the developer has to add a sufficient number of branches to cover all the length cases of the URLs, which will definitely cause a state explosion in the parser graph. Second, the numbers and sizes of PHVs in RMT are usually limited (*e.g.*, there are tens of PHVs in Tofino [22], each is at most 8 bytes), the RMT pipeline can not store the URLs in a PHV even if it can extract it out. Third, carrying out

actions on PHVs in each stage requires large crossbars [112], which are both resource-heavy and performance-sensitive. It might be impossible to fabricate such RMT pipelines with large crossbars to handle arbitrarily long fields like URLs. All these reasons make it challenging for the existing RMT architecture to support general L7 processing.

To this, in Chapter 4, we first analyze the essential reasons why the existing ASIC-based pipeline can not support processing general L7 fields. Then, we narrow down our scope to a specific L7 processing—*i.e.*, L7 dispatch, which is widely used in the service mesh consisting of software proxies—and propose our framework, called QingNiao, to address the issues.

## 3 | Menshen

This chapter presents Menshen, a software-hardware codesign that addresses one aspect of the aforementioned *accessibility*, *i.e.*, multitenancy. To simultaneously and safely run multiple programs on a single device, it is required to support isolation. However, existing high-speed packet-processing pipelines such as RMT provide only limited support for isolation as we discussed in Chapter 2. For example, it is possible to share stateful memory across programs but cannot share other resources like match-action tables [142]. We begin by laying out the requirements for isolation mechanisms on the RMT architecture that are applicable to all resources throughout the pipeline and then we detail the design and implementation of Menshen.

## 3.1 Requirements for Isolation Mechanisms on RMT

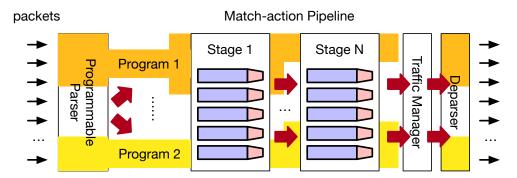

**Figure 3.1:** An example of running multiple programs on a single RMT pipeline. We show the resources allocated to different programs by shading them in the appropriate colors.

As presented in Figure 3.1, the desired isolation mechanisms should guarantee that multiple

programs can be allocated to different resources, and process packets in parallel without impacting each other. Specifically, isolation mechanisms should ensure that:

- 1. **Behavior isolation.** The behavior of one program must not affect the behavior (*i.e.*, input, output, computation, and internal state) of another. This would prevent a faulty or malicious program from adversely affecting other programs. Further, one program should not be able to inspect the behavior of another program.

- 2. **Resource isolation.** A switch/NIC pipeline has multiple resources, *e.g.*, static random-access memory (SRAM) for exact matching and ternary content-addressable memory (TCAM) for ternary matching. Each program should be able to access only its assigned subset of the pipeline's resources and no more. It should also be possible to allocate each resource independent of other resources. For example, an in-network caching program may need large amounts of stateful memory [100] for its caches, but a routing program may need significant TCAM for routing tables.

- 3. **Performance isolation.** Each program should stay within its allotted ingress packets per second and bits per second rates. One program's behavior should not affect the throughput and latency of another program.

- 4. **Lightweight.** The isolation mechanisms themselves must have low overhead so that their presence does not significantly degrade the high performance of the underlying network device. In addition, the extra hardware consumed by these mechanisms must be small.

- 5. **Rapid reconfiguration.** If a program is reconfigured with new packet-processing logic, the reconfiguration process should be quick.

- 6. **No disruption.** If a program is reconfigured, it must not disrupt the behavior of other unchanged programs—especially important in a multi-tenant environment [79].

#### 3.2 Menshen's Approach

As discussed in Chapter 2, RMT is inherently a dataflow architecture, thus *time-sharing* approaches, widely used in the OS/hypervisor, can not be directly applied to RMT. This is mainly because swapping in/out the configurations for different programs to process each packet at the nanosecond level is impossible.

In order to meet its performance goals, RMT's pipelined architecture ensures that processing stages never stall, *i.e.*, they can process a packet every clock cycle. The Menshen design aims to preserve this invariant so that isolation does not come at the cost of performance. To maintain this invariant, Menshen's isolation mechanisms cannot reconfigure stages or change table contents between packets. As a result, Menshen provides isolation by *spatially partitioning* pipeline resources between packet processing programs.

While spatial partitioning is easy for resources, *e.g.*, match-action tables and stateful memory, that are provisioned so they can be allocated at a coarse granularity, it is much more challenging for resources such as key extractors (Chapter 2) which are generally shared across flows. This is because naive approaches to spatially partitioning such shared resources across packet-processing programs would severely reduce the number of resources available to each packet-processing program—and hence the richness and expressiveness of that program.

To see why, consider a case where a key extractor is split between two packet processing programs: in this setting each packet processing program can only use half the key extractor, limiting its key length to half of what it would be able to use were it running on the entire pipeline. Concretely, suppose the original one selects 6 PHVs, if it is evenly partitioned between 2 programs, only 3 PHVs can be selected by each program, which makes the original program that uses 6 PHVs to form keys impossible to run. This problem is of course further exacerbated as we increase the number of packet processing programs sharing the pipeline.

Menshen addresses this problem using *overlays*: we associate a configuration lookup table with

| <b>Applied Mechanism</b> | Targeted Resources                                                                                    |

|--------------------------|-------------------------------------------------------------------------------------------------------|

| Space partitioning       | Match action table entries, stateful memories                                                         |

| Overlays                 | Parsing actions, key extractors, packet header vector (PHV) containers, arithmetic logic units (ALUs) |

Table 3.1: Summary of Menshen's mechanisms.

each shared resource through the RMT pipeline. Menshen adds additional hardware primitives in the form of small tables that store program-specific configurations. As a packet progresses through the pipeline, the packet's program identifier is used as an index into these tables to extract program-specific configurations before processing the packet according to the just extracted configuration. These primitives are similar to the use of *overlays* [37, 4] in embedded systems [54, 1] and earlier PCs [38]. They effectively allow us to bring in different configurations for the same RMT resource, in response to different packets from different programs. For example, in the case of the key extractor, the configuration table contains the instructions that the program uses to construct the key (Chapter 2). Our use of overlays means that we do not need to partition resources including ALUs or PHVs between programs. Instead, the program has exclusive access to all PHVs/ALUs in a stage when processing a packet. Table 3.1 summarizes Menshen mechanisms.

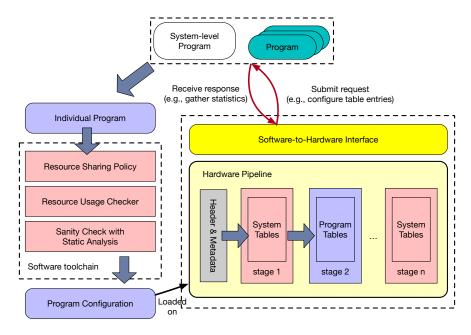

## 3.3 Menshen's Design

At a high level, as shown in Figure 3.2, Menshen combines both the software toolchain with the proposed hardware primitives which are pervasively throughout the RMT pipeline. Specifically, Menshen software (§3.3.1) consists of (1) a system-level program; (2) a compiler that supports resource sharing policy, a resource usage checker, and a sanity checker with static analysis; (3) a software-to-hardware interface like P4Runtime [40], which is used to interact with the underlying hardware pipeline, *e.g.*, configure table entries, gather statistics, etc. Menshen hardware primitives

Figure 3.2: Overview of Menshen's software toolchains and hardware primitives.

(§3.3.2) primarily are in the form of small indirection tables to realize both the techniques of *space* partitioning and overlays.

#### 3.3.1 Menshen Software

Menshen system-level program To hide information about the underlying physical infrastructure (e.g., topology) from tenant programs in a virtualized environment, programs in Menshen can use virtual IP addresses to operate in a shared environment [92]. Here, virtual IP addresses are local and scoped to programs belonging to a particular tenant, regardless of which physical device these programs are on. To support virtual IPs and provide basic services to other programs, Menshen contains a system-level program written in P4-16 that provides common OS-like functionality, e.g., converting virtual IPs to physical IPs, multicast, and looking up physical IPs to find output ports. The system-level program has 3 benefits: (1) it avoids duplication among different programs re-implementing common functions, improving the resource efficiency of the pipeline; (2) it hides underlying physical details (e.g., topology) from each program so that one tenant's programs on

different network devices can form a virtual network [92]; (3) it provides common and useful real-time statistics (*e.g.*, link utilization, queue length, etc.) that can be further used by the packet processing within programs.

The bottom right corner of Figure 3.2 shows how the system-level program is laid out relative to the other user programs. Packets entering the Menshen pipeline are first processed by the system-level program before being handed off to their respective program for program-specific processing. After program-specific processing, these packets enter the system program for a second time before exiting the pipeline. The first time they enter the system-level program, packets can read and update system-level state (*e.g.*, link utilization, packet counters, queue measurements), whereas the second time they enter the system-level program, program-specific packet header fields (*e.g.*, virtual IP address) can be read by the system-level program to determine device-specific information (*e.g.*, output port). In both halves, there is a narrow interface by which programs communicate with the system-level program. This split structure of the system-level program arises directly from the feed-forward nature of the RMT pipeline, where packets typically only flow forward, but not backward. Hence, packets pick up information from the system-level program in the first stage and pass information to the system-level program in the last stage. The non-system programs are sandwiched between these two halves.

The Menshen compiler. Packet-processing pipelines (e.g., RMT [73]) are structured as feed-forward pipelines of programmable units, each of which has limited processing capabilities. This design ensures the *all-or-nothing* property: once a program has been compiled and loaded it can run at up to line rate, while programs that can not run at line rate cannot be compiled. Menshen's compiler follows the same design, and only admits programs that meet line-rate requirements.

The compiler reuses the frontend and midend of the open-source P4-16 reference compiler [39] and creates a new backend similar to BMv2 [5]. This backend has a parser, a single processing pipeline, and a deparser. The compiler takes a program's P4-16 program as input and conducts all the resource usage and static checks described below. Then, for the parser and deparser, it translates

the parser defined in the program into configuration entries for the parser and deparser tables. For the packet-processing pipeline, which consists of match-action tables, it transforms the key in a table to a configuration in the key extractor table, and actions to action table entries according to the opcodes. The compiler also performs dependency checking [73, 101] to guarantee that all ALU actions and key matches are placed in the proper stage, respecting table dependencies.

The Menshen compiler can be extended to support the same packet flowing through different P4 programs belonging to one tenant. The compiler can take multiple P4 programs as input, assign them the same program ID, and allocate them to non-overlapping pipeline stages—similar to how we lay out user and system programs in different stages as in Figure 3.2.

The Menshen resource checker. The Menshen resource checker ensures that each program's resource allocation complies with an operator-specified resource sharing policy (e.g., dominant resource sharing (DRF) [88], or a utility-based [95] policy). In our current design, we check allocations statically because reassigning resources from one program to another disrupts processing for both programs. Instead, we rely on admission control and do not load a program whose resource requirements cannot be met. We leave the question of what is an appropriate resource allocation policy to future work.

The Menshen static checker. To ensure isolation, Menshen's static checker analyzes 3 properties of the program's P4 source code. First, it checks that programs do not modify hardware-related statistics (e.g., link utilization) provided by the system-level program to all programs. Second, programs can not modify their VID. This is because a program can be spread across multiple programmable devices [99, 87], and changes to VIDs by program A on a device can unintentionally affect a program B on a downstream device, where B's real VID happens to be the same as A's modified VID. Third, programs must not recirculate packets and their routing tables should be loop-free. This is because all programs share the same ingress pipeline bandwidth. Recirculating packets or looping them back through multiple devices will degrade the ability of other programs

<sup>&</sup>lt;sup>1</sup>We check loop freedom in the control plane.

to process packets by consuming excessive ingress bandwidth.

The software-hardware interface. The Menshen software-to-hardware interface works similarly to P4Runtime [40] to support interactions (e.g., modifying match-action entries, fetching hardware statistics, etc.) between the Menshen software and the Menshen hardware. However, in addition to P4Runtime's functions, Menshen's software-hardware interface can also be used to reconfigure different hardware resources (we detail the types of Menshen resources in §3.4) in Menshen to reprogram them when a program is added or updated. This allows us to dynamically reconfigure portions of Menshen as program logic changes.

#### 3.3.2 Menshen Hardware

**Figure 3.3:** Menshen builds atop an RMT [73] pipeline. Specifically, Menshen introduces Yellow components and modifies Green ones.

As depicted in Figure 3.3, Menshen's hardware primitives are pervasively throughout the classical RMT [73] pipeline. We first describe the overall Menshen hardware design and then summarize the new isolation primitives added by Menshen.

Menshen expects that a data packet's header carries information identifying what program should process the packet. Currently, in our prototype, this is the VLAN ID (VID) header, which we assume is set by the vSwitch [92], but other fields, *e.g.*, VxLAN ID, can also be used instead. Packets entering Menshen are first handled by a packet filter that discards packets without a VLAN

Figure 3.4: Menshen programmable parser.

ID.<sup>2</sup> Next, a parser extracts the VLAN ID from the packet and applies program-specific parsing to extract program-specific headers from the TCP/UDP payload. The parser then pushes these parsed packet headers into PHV containers that travel through the pipeline of match-action stages.

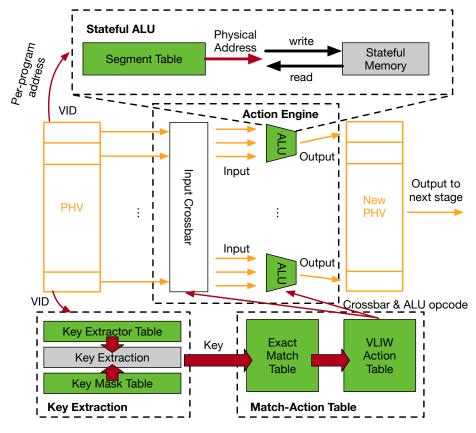

Each stage forms keys out of headers, looks up the keys in a match-action table, and performs actions. At the start of each stage, a key extractor in the stage forms a key by combining together the headers in a program-specific manner. The keys are then concatenated with the program ID and looked up in a match-action table, whose space is partitioned across different programs. If the key matches against a match-action pair in the table, the lookup result is used to index an action table.

Similar to the match-action table, the action table is also partitioned across programs. Each action in the table identifies opcodes, operands, and immediate constants for a very-large instruction word (VLIW), controlling many parallel arithmetic and logic units (ALUs). The VLIW instruction consumes the current PHV to produce a new PHV as input for the next stage. The table's action can modify the persistent pipeline state, stored in stateful memory. Stateful memory is indexed by a physical address that is computed from a local address, obtained from a program's packets. This computation is done by a segment table, which stores the offset and range of each program's slice of stateful memory. We now detail the main components of our design.

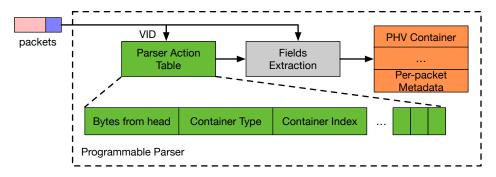

**Parser.** The Menshen parser is driven by a table lookup process similar to the RMT parser [73, 89]. Specifically, whenever a new packet comes in, the program ID is extracted from its VLAN ID

<sup>&</sup>lt;sup>2</sup>The filter can be configured to send control packets without VLAN tags, *e.g.*, BFD packets [7], to the control plane or system-level program (§3.3.1).

Figure 3.5: Menshen processing stage.

prior to parsing the rest of the packet. This program ID is then used as an index into the table that determines how to parse the rest of the packet (Figure 3.4). Each table entry corresponds to multiple parsing actions for a program—one action per extracted PHV container. Each parsing action specifies (1) bytes from head, indicating where in the packet the parser should extract a particular header; (2) container type (e.g., 4-byte container, etc.), indicating how many bytes we should extract; (3) container index, indicating where in the PHV we should put the extracted header into. The parser also sets aside space in the PHV for metadata that is automatically created by the pipeline (e.g., time of enqueue into switch output queues and queueing delay after dequeue) and for temporary packet headers used for computation.

*Key extractor.* Before a stage performs a lookup on a match-action table, a lookup key must be constructed by extracting and combining together one or more PHV containers. This key extraction

process differs between programs in the same stage, and between different stages for the same program. To implement key extraction, just like the parser, we use a key extractor table (Figure 3.5) that is indexed by a packet's program ID. Each entry in this table specifies which PHV containers to combine together to form the key. These PHV containers are then selected into the key using a multiplexer for each portion of the key. To enable variable-length key matching for different programs, the key extractor also includes a key mask table, which also uses the program ID as an index to determine how many bits to pad to a certain fixed key size before lookup.

*Match table.* Each stage looks up the fixed-size key constructed by the key extractor in a match table. Currently, we support only exact-match lookup. The match table is statically partitioned across programs by giving a certain number of entries to each program. To enforce isolation among different programs, the program ID is appended to the key output by the key extractor. This augmented key is what is actually looked up against the entries in the match table; each entry stores both a key and the program ID that the key belongs to. The lookup result is used as index into the VLIW action table to identify a corresponding action to execute.

Action table and action engine. Each VLIW action table entry indicates which fields from the PHV to use as ALU operands (*i.e.*, the configuration of each ALU's operand crossbar) and what opcode should be used for each ALU controlled by the VLIW instruction (*i.e.*, addition, subtraction, etc.). Each ALU outputs a value based on its operands and opcode. There is one ALU per PHV container, removing the need for a crossbar on the output because each ALU's output is directly connected to its corresponding PHV container. After a stage's ALUs have modified its PHV, the modified PHV is passed to the next stage.

Stateful memory. Menshen's action engines can also modify the persistent pipeline state on every packet. Each program is assigned its own address space, and the available stateful memory in Menshen is partitioned across programs. When a program accesses its slice of stateful memory, it supplies a per-program address that is translated into a physical address by a segment table before accessing the stateful memory. To perform this translation, Menshen stores per-program

configuration (*i.e.*, base address and range) in a segment table, which can be indexed by the packet's program ID. Menshen borrows this idea of a segment table from NetVRM's [142, 136] page table, but implements it in hardware instead of programming it in P4 atop Tofino's stateful memory like NetVRM does. This allows Menshen to avoid using scarce Tofino stateful memory to emulate a segment table. Also, by adding segment table hardware to each stage, Menshen avoids sacrificing the first stage of stateful memory for a segment table, instead reclaiming it for useful packet processing. This is unlike NetVRM, which can share stateful memory across programs only from the second stage because the first stage is used for the page table.

**Deparser.** The deparser performs the inverse operation of the parser. It takes PHV containers and writes them back into the appropriate byte offset in the packet header, merges the packet header with the corresponding payload in the packet buffer, and transmits the merged packet out of the pipeline. The format of the deparser table is identical to the parser table and is similarly indexed by a program ID.

Secure reconfiguration. Our threat model assumes that the Menshen hardware and software are trusted, but that data packets that enter the Menshen pipeline are untrusted. Data packets are untrusted because for a switch, they can come from physical machines outside the switch's control and, for a NIC, they can come from tenant VMs sharing the NIC. Hence, the pipeline should be reconfigured only by Menshen software, not data packets.

This is a security concern faced by existing RMT pipelines as well, even without isolation support. Commercial programmable switches solve this problem by using a separate daisy chain [11] to configure pipeline stages. This chain carries configuration commands that are picked up by the intended pipeline stage as the command passes that stage. The chain is only accessible over PCIe, which is connected to the control-plane CPU, but not by Ethernet ports, which carry outside data packets. Hence, the only way to *write* new configurations into the pipeline is through PCIe. The packet-processing pipeline is restricted to just *reading* configurations and using them to implement packet processing. Thus, the daisy chain provides secure reconfiguration by physically separating

reconfiguration and packet processing.

Menshen uses a similar approach by employing a daisy chain for reconfiguration when a program is updated. A special *reconfiguration packet* carries configuration commands for the pipeline's resources (*e.g.*, parser). Our implementation of this daisy chain varies depending on the platform. For our NetFPGA prototype, this daisy chain is connected solely to the switch CPU via PCIe, similar to current switches. For our Corundum NIC prototype, we connect the daisy chain directly to PCIe and use a *packet filter* before our parser to filter out reconfiguration packets from untrusted data packets by ensuring that reconfiguration packets have a specific UDP destination port. An ideal solution would be to use a physically separate interface, *e.g.*, USB or JTAG, for reconfiguring the Menshen pipeline on Corundum, but we found it challenging to implement such a physically separate reconfiguration interface on Corundum. In the evaluation, we show how a daisy chain permits more rapid reconfiguration than an alternative approach of using the AXI-L protocol on an FPGA.

Summary of Menshen's new primitives. The hardware primitives introduced by Menshen on top of an RMT pipeline (Figure 3.3) are the configuration tables for the parser, deparser, key extractor, key mask units and segment table. These tables provide an overlay feature to share the same unit across multiple programs. Specifically, for each unit, Menshen provides a table with a configuration entry per program, rather than one configuration for the whole unit. In addition, Menshen introduces the packet filter to ensure secure reconfiguration. Menshen also modifies match tables, by appending the program ID to the match key and the match-action entries. Finally, Menshen partitions match-action tables and stateful memory across all programs. These primitives ensure that updating one program only affects a single entry (for Menshen resources that use overlays) and only affects a subset of memory (for Menshen resources that use space partitioning), thus allowing us to update one program without disrupting others (§3.5).

ASIC feasibility of Menshen's primitives. Menshen's parser, deparser, key extractor, key mask, and segment tables are small and simple arrays indexed by the program identifier. They can be

**Figure 3.6:** Three optimization techniques applied in Menshen. Numbered circles refer to specific techniques detailed in §3.3.3.

readily realized in SRAM that can support a memory read every clock cycle. The packet filter is a simple combinational circuit that checks if the incoming packet is destined to a specific UDP destination port. Extending the match-action tables in each stage to append a program ID to every entry amounts to modestly increasing the key width in the table. While these new primitives add some additional latency relative to RMT, *e.g.*, to go through the packet filter or reading out the per-program parser configuration, the pipelined nature of RMT means that this additional latency does not impact the packet-forwarding rate.

### 3.3.3 Optimizations for Menshen Hardware

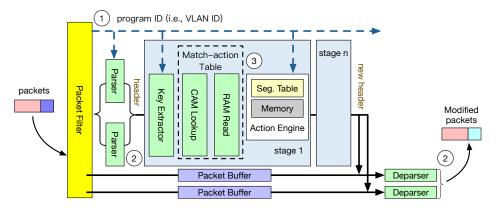

As shown in Figure 3.6, we apply 3 main techniques to optimize the forwarding performance of Menshen: (1) masking RAM read latency, (2) using multiple parsers and deparsers, and (3) increasing pipeline depth. We demonstrate the effect these techniques have on Menshen when evaluating Menshen's throughput in §3.5.2.

1 Masking RAM read latency. The design described in §3.3.2 attaches the module ID to the PHV that is sent from one element (e.g., parser, key extractor) to the next. In this design, we read the module's configuration from SRAM after the PHV arrives, thus incurring a few additional

clock cycles of latency. To optimize this, we mask SRAM access latency by splitting the module ID from the PHV and sending the module ID to the next element *ahead of time*. The PHV follows the module ID, and thus the module configuration at a stage can be read concurrently with the PHV being transmitted to that stage.

2 *Multiple parsers and deparsers*. In §3.3.2's design, there is one parser, deparser, and packet buffer. The parser extracts and parses the header and puts the full packet in the packet buffer. Then the deparser takes the modified headers from the last stage, uses them to overwrite the relevant portions of the full packet in the packet buffer, and sends out the packet.

Our optimized design uses multiple parallel parsers, deparsers, and packet buffers to improve throughput. Deparsing is the most expensive operation as any position within the PHV container might be modified, and thus any part of the packet header (128 bytes in our implementation) might need to be updated. Furthermore, deparsing has to process both the packet header and the payload. Therefore, we use 4 parallel deparsers and 2 parsers. We also associate a separate packet buffer with each deparser.

On ingress, the packet filter tags each packet with a packet buffer number (0–3) in round robin order. It also round robins incoming packets to the 2 parsers. The last pipeline stage uses the packet buffer tag to determine which packet buffer's packet the last stage's modified PHV should be combined with. Each packet buffer's deparser combines the earliest packet from the packet buffer along with the last stage's most recently modified PHV for that buffer.

3 Deep pipelining. With careful digital design, in Menshen's implementation, we can pipeline each element (e.g., match-action table) into several sub-elements to improve throughput. For example in Figure 3.6, we divide the match-action table into CAM-lookup and action-RAM-read sub-elements. In this specific example, this allows us to process a PHV every 2 clock cycles at each sub-element rather than every 4 clock cycles at the whole match-action table.

## 3.4 Implementation

### 3.4.1 Menshen Software

The Menshen compiler reuses the open-source P4-16 reference compiler [39] and implements a new backend extension in 3773 lines of C++. It takes the program written in P4-16 together with resource allocation as the inputs, and generates per-program configurations for Menshen hardware. Specifically, it (1) conducts resource usage checking to ensure every program's resource usage is below its allocated amount; (2) places the system-level program's (120 lines of P4-16) configurations in the first and last stages in the Menshen pipeline; and (3) allocates PHV containers to the fields shared between the system-level and other programs so that the other programs can be sandwiched between the two halves of the system-level program (§3.3.1). The Menshen software-to-hardware interface is written in Python. It configures Menshen hardware by converting program configurations to reconfiguration packets.

### 3.4.2 Menshen Hardware

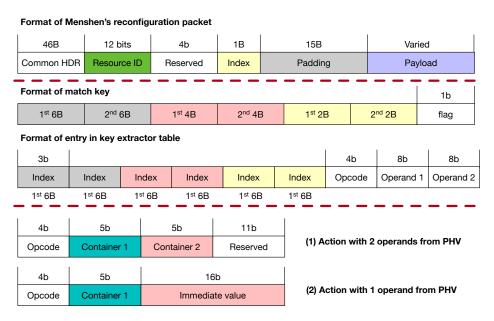

To implement Menshen hardware, we first built a baseline RMT implementation for an FPGA. Menshen includes (1) a packet filter to filter out reconfiguration packets from data packets using a specific predefined UDP destination port (*i.e.*, 0xf1f2), (2) a programmable parser, (3) a programmable RMT pipeline with 5 programmable processing stages, (4) a deparser, and (5) a separate daisy-chain pipeline for reconfiguration. It also includes Menshen's primitives for isolation. We have integrated it into both the Corundum NIC [83] and the NetFPGA reference switch [144]. The Menshen code base together with the optimizations (§3.3.3) consists of 9975 lines of Verilog. Of this, 3098 and 3226 lines are for handling data bus widths of 512 bits (Corundum) and 256 bits (NetFPGA) respectively. 3651 lines are for the common blocks, *e.g.*, key extractor, etc. Below, we describe our hardware implementation in more detail. Figure 3.7 shows the formats of Menshen's

Figure 3.7: Formats of Menshen's packets and tables.

packets and tables.

**PHV format.** Menshen's PHV has 3 types of containers of different sizes, namely 2-byte, 4-byte and 6-byte containers. Each type has 8 containers. Also, we allocate and append an additional 32 bytes to store platform-specific metadata (e.g., an indication to drop the packet, destination port, etc.), which results in a PHV length of 128 bytes in total. Thus, we have a total of 3\*8+1=25 PHV containers. To prevent any possibility of PHV contents leaking from one program to another, the PHV is zeroed out for each incoming packet.

Reconfiguration packet format. Figure 3.7 shows the format of Menshen reconfiguration packets. The reconfiguration packet is a UDP packet with the standard UDP, Ethernet, VLAN, and IP headers. Within the UDP payload, a 12-bit resource ID indicates which hardware resource within which stage should be updated (e.g., key extractor table in stage 3). To reconfigure the resource, the table storing the configuration for this resource must be updated by writing the entry stored within the reconfiguration packet's payload at the location specified by the 1-byte index field in the reconfiguration packet header. The UDP destination port field determines whether the reconfiguration packet is valid or not.

Packet filter. The packet filter has 2 registers that can be accessed by the Menshen software via Xilinx's AXI-Lite protocol [61]: (1) a 4-byte reconfiguration packet counter, which monitors how many reconfiguration packets have passed through the daisy chain; (2) a 32-bit bitmap, which indicates which program is currently being updated (e.g., bit 1 stands for program 1, bit 2 for program 2, etc.). During the reconfiguration of a program, via the software-to-hardware interface, the Menshen software reads the reconfiguration packet counter. It then writes the bitmap to reflect the program ID M of the program currently being updated. The bitmap is then consulted on every packet to drop data packets from M until reconfiguration completes, so that M's "in-flight" packets aren't incorrectly processed by partial configurations.

Then, the Menshen software sends all reconfiguration packets embedded with the predefined UDP destination port to the daisy chain. Finally, it polls the reconfiguration packet counter to check if reconfiguration is over and then zeroes the bitmap so that M's packets are no longer dropped. Reconfiguration packets may be dropped before they reach the RMT pipeline. This can be detected by polling the reconfiguration packet counter to see if it has been correctly incremented or not. If it hasn't been incremented correctly, then the entire reconfiguration process restarts with M's packets being dropped until reconfiguration is successful.

**Programmable parser/deparser.** We currently support per-program packet header parsing in the first 128 bytes of the packet. These 128 bytes also include the headers common to all programs (e.g., Ethernet, VLAN, IP, and UDP). We design the parser action for each parsed PHV container as a 16-bit action. The first 3 bits are reserved. The next 7 bits indicate the starting extraction position in bytes from byte 0. These 7 bits can cover the whole 128-byte length. Then, the next 2 bits and 3 bits indicate the container type (2, 4, or 6 byte) and number (0–7) respectively. The last bit is the validity bit. For each program, we allocate 10 such parser actions (i.e., to parse out at most 10 containers), resulting in a 160-bit-wide entry for the parser action table.

We note that we only parse out fields of a packet into PHV containers, if those fields are actually used as part of either keys or actions in match-action tables. Before packets are sent out, the

deparser pulls out the full packet (including the payload) from the packet buffer and only updates the portions of the packet that were actually modified by table actions. This approach allows us to reduce the number of PHV containers to 25 because packet fields that are never modified or looked up by the Menshen pipeline need not travel along with the PHV.

Key extractor. The key for lookup in the match-action table is formed by concatenating together up to 2 PHV containers each of the 2-byte, 4-byte, and 6-byte container types. Hence the key can be up to 24 bytes and 6 containers long. Since there are 8 containers per type, the key extraction table entry for each program in each stage uses  $log_2(8)*6=18$  bits to determine which container to use for the 6 key locations. Additionally, the key extractor is also used to support conditional execution of actions based on the truth value of a predicate of the form A OP B, where A and B are packet fields and OP is a comparison operator. For this purpose, each key extractor table entry also specifies the 2 operands for the comparison operation and the comparison opcode. The opcode is a 4-bit number, while the operands are 8 bits each. The operands can either be an immediate value or refer to one of the PHV containers. The result of the predicate evaluation adds one bit to the original 24 byte key, bringing the total key length to 24\*8+1=193 bits. Because not all keys need to be 193 bits long, we use a 193-bit-wide mask table. Each entry in this table denotes the validity of each of the 193 key bits for each program in each stage. This is somewhat wasteful and can be improved by storing validity information within the key extractor table itself.

Exact match table. To implement the exact match table, we leverage the Xilinx CAM block [64]. This CAM matches the key from the key extractor program against the entries within the CAM. As discussed in §3.3.2, to ensure isolation between different programs, we append the program ID (i.e., VLAN ID) to each entry, which means that the CAM has a width of 193 + 12 = 205 bits. The lookup result from the CAM is used to index the VLIW action table. The action is designed in a 25-bit format per ALU/container (Figure 3.7). As we have 24 + 1 = 25 PHV containers, the width of the VLIW action table is 25 \* 25 = 625 bits. The Xilinx CAM block simplifies the implementation of an exact-match table and can also easily support ternary matches if needed.

| Operation | Description                                            |

|-----------|--------------------------------------------------------|

| add/sub   | Add/subtract between containers                        |

| addi/subi | Add/subtract an immediate to/from container            |

| set       | Set a container to an immediate value                  |

| load      | Load a value from stateful memory                      |

| store     | Store a value to stateful memory                       |

| loadd     | Load value from stateful memory, add 1, and store back |

| port      | Set destination port                                   |

| discard   | Discard packet                                         |

Table 3.2: Supported operations in Menshen's ALU.

Action engine. The crossbar and ALUs in the action engine use the VLIW actions to generate inputs for each ALU and carry out per-ALU operations. ALUs support simple arithmetic, stateful memory operations (e.g., loads and stores), and platform-specific operations (e.g., discard packets) (Table 3.2). The formats of these actions are shown in Figure 3.7. Additionally, in stateful ALU processing, each entry in the segment table is a 2-byte number, where the first byte and second byte indicate memory offset and range, respectively.

*Menshen primitives.* Menshen's isolation primitives (*e.g.*, key-extractor and segment tables) are simple arrays implemented using the Xilinx Block RAM [63] feature. All Menshen's hardware resources are detailed in Table 3.3.

### 3.4.3 Corundum and NetFPGA Integrations

We have integrated Menshen into 2 FPGA platforms: one for the NetFPGA platform that captures the hardware architecture of a switch [144], and another for the Corundum platform that captures the hardware architecture of a NIC [83]. Menshen's integration on Corundum [83] is based on a 512-bit AXI-S [62] data width and runs at 250 MHz. Although Menshen's pipeline can be integrated into both the sending and receiving path, in our current implementation, we have integrated Menshen into only Corundum's sending path, *i.e.*, PCIe input to Ethernet output.

| Hardware Resource         | Description                                        |

|---------------------------|----------------------------------------------------|

| Packet Filter             | A 32-bit bitmap,                                   |

| T acket l'illei           | and a 4-byte reconfiguration packet counter        |

|                           | 2-byte, 4-byte, 6-byte containers,                 |

| PHV                       | each type has 8 containers                         |

|                           | a 32-byte container for platform-specific metadata |

| Parsing action            | 16 bits wide                                       |

| Parser and deparser table | 10 parsing actions, 160 bits wide, 32 entries deep |

| Key extractor table       | 38 bits wide, 32 entries deep                      |

| Key mask table            | 193 bits wide, 32 entries deep                     |

| Exact match table         | 205 bits wide, 16 entries deep                     |

| ALU Action                | 25 bits wide                                       |

| VLIW action table         | 25 ALU actions, 625 bits wide, 16 entries deep     |

| Segment table             | 16 bits wide, 32 entries deep                      |

| Stages                    | 5                                                  |

| Program ID                | 12 bits                                            |

**Table 3.3:** Hardware resources in Menshen

Menshen on NetFPGA [144] uses a 256-bit AXI-S [62] data width and runs at 156.25 MHz.

On the Corundum NIC platform, we insert a 1-bit discard flag, while on the NetFPGA switch platform, we insert a 1-bit discard flag and 128-bit platform-specific metadata, *i.e.*, source port, destination port and packet length, into the PHV's metadata field. A 4-bit one-hot encoded tag indicates the packet buffer (§3.3.3). The table depth in Menshen's parser, key extractor, key mask, page, and deparser tables affects the maximum number of programs we can support and is currently 32. The depth of CAM and VLIW action table directly influences the amount of match-action entries and VLIW actions that can be allocated to all programs. Due to the open technical challenge of implementing CAMs on FPGAs efficiently [120, 98], we set their depth to 16 in each stage. While 16 is a small depth, the depth can be improved by using a hash table, rather than a CAM, for exact matching, *e.g.*, cuckoo hashing [117].

| Program             | Description                                      |

|---------------------|--------------------------------------------------|

| CALC [41]           | return value based on parsed opcode and operands |

| Firewall [41]       | stateless firewall that blocks certain traffic   |

| Load Balancing [41] | steer traffic based on 4-tuple header info       |

| QoS [41]            | set QoS based on traffic type                    |

| Source Routing [41] | route packets based on parsed header info        |

| NetCache [100]      | in-network key-value store                       |

| NetChain [99]       | in-network sequencer                             |

| Multicast [41]      | multicast based on destination IP address        |

Table 3.4: Evaluated use cases.

# 3.5 Evaluation

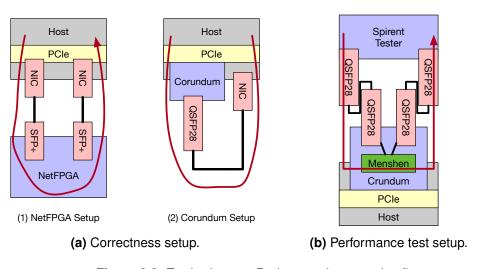

Figure 3.8: Testbed setup. Red arrow shows packet flow.

In §3.5.1, we show that Menshen can meet our requirements (§3.1): it can be rapidly reconfigured, is lightweight, provides behavior isolation, and is disruption-free. Menshen achieves performance isolation by (1) assuming packets exceed a minimum size (to guarantee line rate) and (2) forbidding recirculation. If either is violated, hardware rate limiters can be used to limit each program's packet/bit rate. It achieves resource isolation by ensuring that a table entry for a resource (e.g., parser) is allotted to at most one program. In §3.5.2, we evaluate the current performance of

Menshen in terms of throughput and latency.

Experimental setup. To demonstrate Menshen's ability to provide multi-program support, we picked 6 tutorial P4 programs [41], as detailed in Table 3.4, together with simplified versions of NetCache [100] and NetChain [99].<sup>3</sup> The system-level program provides basic forwarding and routing, with multicast logic integrated into it. Menshen's parameters are detailed in §3.4 and summarized in Table 3.3 in the §3.4.2.

Testbed. Our experimental setup is depicted in Figure 3.8. We evaluate Menshen based on our Corundum and NetFPGA integrations as described in §3.4.3. For the switch platform experiments on NetFPGA, we use a single quad-port NetFPGA SUME board [33], where two ports are connected to a machine equipped with an Intel Xeon E5645 CPU clocked at 2.40 GHz and a dual-port Intel XXV710 10/25GbE NIC. For the NIC platform experiments on Corundum, we use a single Xilinx Alveo U250 board [3], where one port is with Menshen for the transmitting path and this port is connected to a 100 GbE NIC as the receiving path. Both setups are used to check Menshen's correctness (§3.5.1). For NetFPGA performance tests (§3.5.2), we use the host as a packet generator. For Corundum performance tests (§3.5.2), we internally connect its receiving and transmitting path, and use the Spirent tester [49] to generate traffic.

### 3.5.1 Does Menshen meet its requirements?

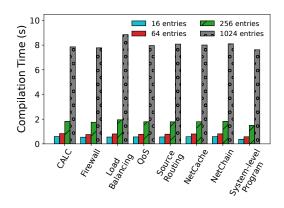

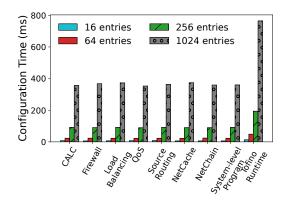

Menshen can be rapidly reconfigured. Reconfiguration time includes both the software's compilation time (Figure 3.9) and the hardware's configuration time (Figure 3.10); we evaluate each separately. When a program is compiled, the compiler needs to generate both configuration bits for various hardware resources as well as match-action entries for the tables the program looks up. These match-action entries can and will be overwritten by the control plane, but we need to start out with a new set of match-action entries for a program to ensure no information leaks from a previous program.

<sup>&</sup>lt;sup>3</sup>Our versions of NetChain and NetCache do not include some features such as tagging hotkeys.

Figure 3.9: Compilation time of Menshen.

Figure 3.10: Configuration time of Menshen.

Hence, every time a program is compiled, the compiler also generates match-action entries. Within an exact match table, these entries must be different from each other to prevent multiple lookup results. As a result shown in Figure 3.9, Menshen's compilation time increases with the number of match-action entries in the program. To contextualize this, Menshen's compile times (few seconds) compare favorably to compile times for Tofino (~10 seconds for our use cases) and FPGA synthesis times (10s of minutes). We note that this is an imperfect comparison: our compiler performs fewer optimizations than either the Tofino or FPGA compilers and our targets are simpler. That said, compilation can happen offline, and hence it is not as time-sensitive compared to run-time reconfiguration which is more important as new configurations should take effect as quickly as possible.