# SYNTHESIZING EXECUTABLE PROGRAMS FROM REQUIREMENTS

by

Cory Plock

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Computer Science New York University May 2008

Benjamin Goldberg

### © Cory Plock

### All Rights Reserved, 2008

# **Dedication**

For my beloved wife Lizette, who gave me the strength to continue when the end wasn't anywhere in sight. Also for my parents, whose love, support, and inspiration have guided me through the past many years. Finally, for my brother Michael, whose love, encouragement, and sense of humor have propelled me through all the tough times.

# Acknowledgments

I would like to thank my advisor Ben Goldberg and co-advisor Hillel Kugler for their guidance, support, and encouragement over the past many years. I would like to also extend my gratitude to Amir Pnueli for taking the time to provide research guidance, and to Anina Karmen for going far above and beyond the call of duty. Thanks to Bonnie MacKellar, who introduced me to the world of research as an undergraduate and always challenged me to excel. Finally, thank you to Mr. Charles McFarlane, who saw talent in me that I couldn't see myself, and without whom I couldn't have reached this point.

## Abstract

Automatic generation of correct software from requirements has long been a "holy grail" for system and software development. According to this vision, instead of implementing a system and then working hard to apply testing and verification methods to prove system correctness, a system is rather built correctly by construction. This problem, referred to as synthesis, is undecidable in the general case. However, by restricting the domain to decidable subsets, it is possible to bring this vision one step closer to reality.

The focus of our study is reactive systems, or non-terminating programs that continuously receive input from an external environment and produce output responses. Reactive systems are often safety critical and include applications such as anti-lock braking systems, auto-pilots, and pacemakers. One of the challenges of reactive system design is ensuring that the software meets the requirements under the assumption of unpredictable environment input. The behavior of many of these systems can be expressed as regular languages over infinite strings, a domain in which synthesis has yielded successful results.

We present a method for synthesizing executable reactive systems from formal requirements. The object-oriented requirements language of Live Sequence Charts (LSCs) is considered. We begin by establishing a mapping between various subsets of the language and finite-state formal models. We also consider LSCs which can express time constraints over a dense-time domain. From one of these models, we show how to formulate a winning strategy that is guaranteed to satisfy the requirements, provided one exists. The strategy is realized in the form of a controller which guides the system in choosing only non-violating behaviors. We describe an implementation of this work as an extension of an existing tool called the Play-Engine.

# Contents

| Dedication |         |               |                         |     |  |  |  |

|------------|---------|---------------|-------------------------|-----|--|--|--|

| Ac         | cknow   | vledgme       | ents                    | v   |  |  |  |

| AJ         | bstrac  | :t            |                         | vi  |  |  |  |

| Li         | st of l | Figures       |                         | xii |  |  |  |

| Li         | st of [ | <b>Fables</b> |                         | xiv |  |  |  |

| In         | trodu   | ction         |                         | 1   |  |  |  |

| 1          | Req     | uireme        | nts Languages           | 7   |  |  |  |

|            | 1.1     | Synch         | ronous Languages        | 8   |  |  |  |

|            | 1.2     | Visual        | Modeling                | 9   |  |  |  |

|            |         | 1.2.1         | Message Sequence Charts | 9   |  |  |  |

|            |         | 1.2.2         | Multiple MSCs           | 11  |  |  |  |

|            |         | 1.2.3         | Shortfalls              | 12  |  |  |  |

|            | 1.3     | Live S        | equence Charts          | 14  |  |  |  |

|            |         | 1.3.1         | Example                 | 15  |  |  |  |

|            |         | 1.3.2         | Justification for Use   | 18  |  |  |  |

| 2 | LSC  | Requir  | rements                          | 21 |

|---|------|---------|----------------------------------|----|

|   | 2.1  | Object  | Systems                          | 21 |

|   |      | 2.1.1   | Definitions                      | 22 |

|   |      | 2.1.2   | Relationship to LSCs             | 23 |

|   | 2.2  | Live Se | equence Charts                   | 23 |

|   | 2.3  | Livene  | SS                               | 25 |

|   |      | 2.3.1   | Hot and Cold Temperature         | 26 |

|   |      | 2.3.2   | More on Cold Temperatures        | 28 |

|   |      | 2.3.3   | Warm Temperatures                | 28 |

|   |      | 2.3.4   | Conditions                       | 32 |

|   | 2.4  | Variab  | les and Properties               | 33 |

|   | 2.5  | Events  |                                  | 34 |

|   | 2.6  | Tempo   | ral Event Ordering               | 37 |

|   | 2.7  | Visible | Events                           | 37 |

|   | 2.8  | The LS  | SC Language                      | 38 |

|   |      | 2.8.1   | Cuts                             | 38 |

|   |      | 2.8.2   | Enablement                       | 39 |

|   |      | 2.8.3   | Assignments and Conditions       | 40 |

|   |      | 2.8.4   | Successor Cuts                   | 41 |

|   |      | 2.8.5   | Runs & Computations              | 42 |

|   |      | 2.8.6   | Hidden Events                    | 43 |

|   |      | 2.8.7   | Chart Satisfaction and Violation | 45 |

|   | 2.9  | Examp   | le                               | 45 |

|   | 2.10 | Multip  | le LSC Requirements              | 48 |

|   | 2.11 | Self-Sp | pawning LSCs                     | 50 |

| 3 | Tim  | ed LSC Requirements 5                   | 52 |

|---|------|-----------------------------------------|----|

|   | 3.1  | Introduction to Time                    | 52 |

|   | 3.2  | Related Work                            | 53 |

|   | 3.3  | Single Discrete-Time LSCs               | 53 |

|   |      | 3.3.1 Definition                        | 54 |

|   |      | 3.3.2 Timed Cuts                        | 55 |

|   |      | 3.3.3 Discrete-Time Assertions          | 56 |

|   |      | 3.3.4 Successor Cuts                    | 56 |

|   |      | 3.3.5 Runs and Computations             | 57 |

|   | 3.4  | Single Dense-Time LSCs                  | 58 |

|   |      | 3.4.1 Successor Cuts                    | 50 |

|   |      | 3.4.2 Runs and Computations             | 50 |

|   | 3.5  | Multiple Dense-Time LSCs                | 51 |

|   |      | 3.5.1 Runs and Computations             | 53 |

|   | 3.6  | Timed LSC Example                       | 54 |

| 4 | From | n Requirements to Specifications        | 67 |

|   | 4.1  | Related Work                            | 58 |

|   | 4.2  | Single Discrete-Time LSC Specifications | 59 |

|   |      | 4.2.1 State Space                       | 59 |

|   |      | 4.2.2 Büchi Automata                    | 70 |

|   |      | 4.2.3 Translation                       | 71 |

|   |      | 4.2.4 Example                           | 77 |

|   | 4.3  | Dense-Time LSC Specifications           | 78 |

|   |      | 4.3.1 Timed Automata                    | 79 |

|   |      | 4.3.2 Translation                       | 82 |

|   | 4.4  | Multiple LSC Specifications    9            | 1 |

|---|------|---------------------------------------------|---|

|   |      | 4.4.1 Translation                           | 2 |

|   | 4.5  | Non-Deterministic Hidden Events             | 5 |

| 5 | Auto | omata-Based Synthesis 9                     | 7 |

|   | 5.1  | Related Work                                | 8 |

|   | 5.2  | Smart Play-Out                              | 9 |

|   |      | 5.2.1 An Example                            | 1 |

|   | 5.3  | Overview                                    | 2 |

|   | 5.4  | Game Structures                             | 3 |

|   | 5.5  | Game Rules                                  | 4 |

|   | 5.6  | The Synthesis Problem                       | 6 |

|   |      | 5.6.1 Definitions                           | 7 |

|   |      | 5.6.2 Main Result                           | 7 |

|   |      | 5.6.3 Algorithm                             | 8 |

|   | 5.7  | Example                                     | 3 |

|   | 5.8  | Finding the Winning Strategy                | 5 |

| 6 | Sym  | bolic LSC Synthesis 11                      | 8 |

|   | 6.1  | Symbolic Game Structures                    | 9 |

|   |      | 6.1.1 Dependent vs. Independent Transitions | 1 |

|   |      | 6.1.2 Deadlock                              | 3 |

|   | 6.2  | Definitions                                 | 4 |

|   |      | 6.2.1 Controllable Predecessors             | 5 |

|   |      | 6.2.2 Realizability & Winning Strategy      | 6 |

|   | 6.3  | Smart Play-Out                              | 7 |

|              | 6.4 | Main R    | esult                        | 128 |  |  |  |  |

|--------------|-----|-----------|------------------------------|-----|--|--|--|--|

|              |     | 6.4.1     | Variables                    | 129 |  |  |  |  |

|              |     | 6.4.2     | Transitions                  | 131 |  |  |  |  |

|              |     | 6.4.3     | Initial & Winning Conditions | 133 |  |  |  |  |

|              | 6.5 | Implem    | entation & Results           | 135 |  |  |  |  |

| 7            | Con | tribution | ns and Future Work           | 138 |  |  |  |  |

|              | 7.1 | Summa     | ry                           | 138 |  |  |  |  |

|              | 7.2 | Contrib   | utions                       | 139 |  |  |  |  |

|              | 7.3 | Future I  | Directions                   | 141 |  |  |  |  |

|              |     | 7.3.1     | Time Consumption             | 142 |  |  |  |  |

|              |     | 7.3.2     | System Choices               | 143 |  |  |  |  |

|              |     | 7.3.3     | Unrealizability              | 143 |  |  |  |  |

|              |     | 7.3.4     | Synthesis with Time          | 144 |  |  |  |  |

| Appendix     |     |           |                              |     |  |  |  |  |

| Bibliography |     |           |                              |     |  |  |  |  |

# **List of Figures**

| 1.1 | Basic Message Sequence Chart                            | 10  |

|-----|---------------------------------------------------------|-----|

| 1.2 | MSC Requirements using hMSCs and Sequential Composition | 12  |

| 1.3 | Cellular Phone Scenario: Turn On                        | 16  |

| 1.4 | Cellular Phone Scenario: Turn Off                       | 18  |

| 2.1 | LSCs with Fairness                                      | 27  |

| 2.2 | LSC with Warm Temperatures                              | 31  |

| 2.3 | Hidden Event Generation                                 | 44  |

| 2.4 | Fairness Free Universal LSC                             | 46  |

| 2.5 | Self-Spawning LSC                                       | 50  |

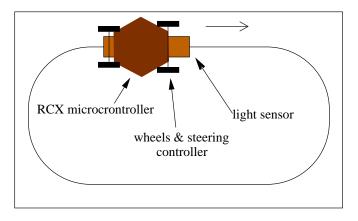

| 3.1 | Robot Test Pad                                          | 64  |

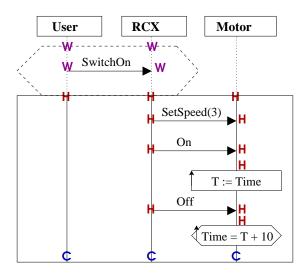

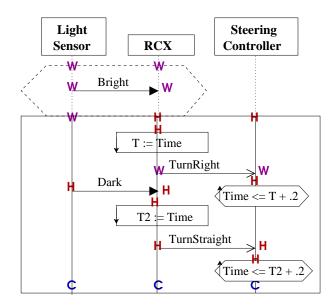

| 3.2 | Scenario 1: Switching Robot On                          | 65  |

| 3.3 | Scenario 2: Turning Right                               | 66  |

| 4.1 | LSC Simultaneous regions                                | 70  |

| 4.2 | Büchi Automaton of Fig. 4.1                             | 78  |

| 4.3 | Timed Automata Successor Sequence Problem               | 84  |

| 5.1 | LSC Requirements for Smart Play-Out                     | 101 |

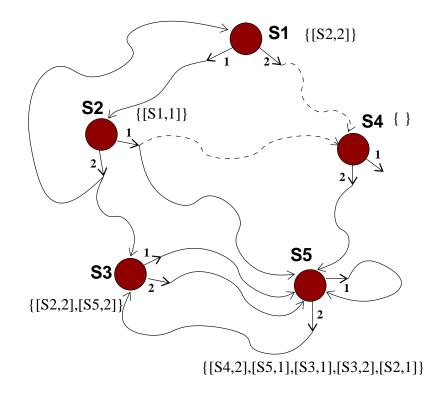

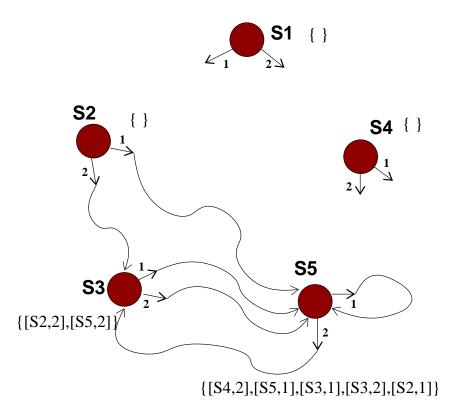

| 5.2 | Finding Uncontrollable States                           | 114 |

|     |                                                         |     |

| 5.3 | Removing Paths to Uncontrollable States | • | • | <br>• | • | • | • | • | • | • | • | • | • | <br>115 |

|-----|-----------------------------------------|---|---|-------|---|---|---|---|---|---|---|---|---|---------|

| 5.4 | Forward Controllable Set                |   |   |       |   |   |   | • |   |   |   |   |   | <br>116 |

# **List of Tables**

| 6.1 | Input LSC Requirements Data   | • | • | • | • | • | • | • | • | <br>• | • | • | • | • | • | • | • | • | • • | 136 |

|-----|-------------------------------|---|---|---|---|---|---|---|---|-------|---|---|---|---|---|---|---|---|-----|-----|

| 6.2 | Synthesis Runtime Performance |   |   | • | • |   | • |   | • | <br>• | • | • |   |   | • |   |   | • |     | 136 |

### Introduction

The general consensus among those in the software engineering community is that object-oriented programming—particularly its role in enabling software reuse—is a favorable programming paradigm. Many practitioners are attracted to the idea that one can write software, test it, and then deliver it to another developer without the recipient having to concern herself with implementation details. The recipient can instead simply refer to "the interface," which usually amounts to a textual description of what the object is supposed to do.

Creating objects for other developers to use is a process which lends itself to intraobject design practices. That is, designs which focus primarily on the data members of the object and how the data changes over time with respect to method calls. In fact, considerable effort goes into testing individual objects. However, comparatively little attention seems to be paid to inter-object issues in practice—that is, the question of whether objects properly interact with each other.

This gives rise to large libraries of objects whose inter-object behavior is unclear, despite a clear understanding of each individual object's behavior. The inevitable consequence is software which does not behave as expected. This could possibly be explained, in part, by the fact that popular modeling languages such as UML are weak on expressing object interactions. Arguably, intra-object constructs such as Statecharts tend to be taken more seriously among developers than the inter-object counterparts, e.g., sequence diagrams.

The problem of arriving at correct software extends beyond the inter-object vs. intra-object design issue. Indeed, even in the presence of perfect designs, any implementation process that incorporates human intervention on a large scale is virtually guaranteed to introduce errors into the final implementation. Errors can range from behavior which was not intended by the requirements author(s) to straight-out system crashes. We therefore find it reasonable to explore the possibility of removing at least some of the human component of software implementation.

#### **Software Lifecycle**

The software development process begins with the *requirements* phase, referring to the gathering of information which describes how a final program is intended to behave. The output of the *specification* phase delivers a set of software blueprints, describing how the requirements are to be carried out. The *implementation* phase refers to the process of writing instructions (e.g., in a programming language), part of which often involves the compilation to machine level code. The *testing* phase amounts to formal or informal verification of the implemented software with respect to the requirements.

A correct executable program is the desired outcome of this process. A correct program, with respect to the requirements, carries out all intended behaviors and no unintended ones. In order to be classified as incorrect, a program need only carry out just one unintended behavior or fail to carry out one intended behavior.

Incorrect behavior has the potential to be catastrophic in the case of safety critical software systems. Past incidents confirm that our fears are justified. For example, energy management software—later found to be incorrect [Jes04]—failed to alert officials of a problem that contributed to the largest rolling power outage in the history of the northern United States in August, 2003. In September 1999, a relatively simple unit conversion error caused the untraceable disappearance of NASA's Mars Climate Orbiter, marking a total economic loss of over 327 million dollars [NAS99].

Researchers and engineers have struggled for years to develop software design and implementation methodologies which lead to correct executable programs. Despite numerous useful research results and programming methodologies that have emerged over the years, a general solution for consistently achieving correctness remains elusive for all but the most trivial programming tasks.

Requirements can take on a variety of forms ranging between prose to a formal description. In practice, most fall somewhere in between. One popular requirements methodology is the Object Management Group's standardized Unified Modeling Language (UML)[BRJ99], and more recently, UML 2.0.

One typical problem with requirements is *incompleteness*, characterized by their inability to classify all possible behaviors as good or bad. For example, requirements are often biased toward *sunny day scenarios*, whereby "normal" behavior is described in full detail, but exceptional behavior—most often caused by unexpected input—is not. Failure to account for unexpected inputs at the requirements level leads to behavior

whose correctness is unknown. In some cases (e.g., software crashes) these behaviors are obviously bad. Other cases are more subtle in the sense that some may view the behaviors as correct, while others may not. In the absence of a precise blueprint, it is impossible to determine.

Even when the requirements are complete, the final implementation can still nevertheless be incorrect. Experience shows that this is attributable to human error in many cases, and can be traced to any phase of the software life-cycle which involves human intervention. Specific causes can include poor coding technique, miscommunication, incorrect operating assumptions, language barriers, or a multitude of other factors. Also, requirements in written form may not necessarily agree with the intentions of the person who wrote them—the designer may have overlooked certain subtleties in the description, for example.

Lacking any better methods at their immediate disposal, design teams often just try their best at writing correct code with the hope that creating and executing test cases will capture most errors. While better solutions may exist, whether it be in practice or in theory, most software engineers lack knowledge of formal verification techniques.

Of particular interest to us are *reactive systems*, or non-terminating programs which perpetually respond to environment inputs [HP85]. These systems are found everywhere and include toasters, microwaves and alarm clocks, for example. Many safety critical applications are reactive too, including anti-lock braking systems, pace-makers, and aircraft autopilots—all of which, if not correct, can lead to catastrophic consequences.

In most reactive systems, assumptions about external environment behavior must

necessarily be limited. By this, we mean that one cannot assume that the environment will cooperate in delivering inputs precisely as the software designer expected. These systems are environment-driven insofar as they are expected to respond to the environment, not vice versa. The burden is therefore on the system to respond to each environment input correctly, in the sense that the totality of these behaviors—those of both the system *and* environment—satisfies the requirements.

In this work, we consider a subset of the object-oriented requirements language Live Sequence Charts (LSCs) [DH01]. LSCs express inter-object behaviors using *scenarios*, where emphasis is placed on the interaction between objects in the system. This is in contrast to the more usual intra-object approach which focuses on the internal behaviors of each object. One of our reasons for choosing LSCs is that behaviors can be described visually, in a way that many people—even non-developers—can understand. The visual aspect of LSCs does not come at the cost of precision or clarity, as as LSCs describe reactive behaviors precisely.

An ambitious vision is presented in [Har00], whereby fully executable code could someday be generated seamlessly from requirements. According to this vision, the object-oriented scenario-based requirements language of LSCs would also serve as the final implementation. The research community has responded rather positively to this vision by proposing a number of approaches to reaching this goal. See, for example, [HM01, KW01, BH02, BS03b, Gil03, PGZ05].

### Contributions

We proceed according to the above vision by presenting a method for synthesizing executable reactive systems directly from requirements. Our work is broken down into two major parts.

We first present a method for the automatic translation of requirements to specifications. That is, a translation from the visual domain of LSCs to deterministic Büchi automata. We then extend the result to include single LSC models which can express rational time constraints over a dense time domain, and present a method for translating from this domain to deterministic timed Büchi automata. We conclude with one of the main contributions of this work, a translation from multiple-LSC requirements over a dense time domain to deterministic timed Büchi automata.

The second part discusses two solutions for performing controller synthesis on LSCs, starting from a specification. The first is an algorithm which abstracts away certain specification details to focus on the general framework for solving the problem intuitively for LSCs. Secondly, we describe an approach for modifying an existing specification to be suitable for input to a controller synthesis algorithm. We also describe a modification to the original result which permits us to express LSC behaviors more naturally than we could otherwise.

A more detailed discussion of our contributions appears in Chapter 7, after the reader has become familiarized with the material in this work.

## **Chapter 1**

# **Requirements Languages**

The first stage in the software life-cycle is the creation of *requirements* that express a design team's behavioral expectations of a future application. Our goal is to automatically translate requirements to executable code, so it is essential that we only consider requirements which are precisely defined. A *requirements language* is used for authoring requirements, similar to the way a programming language is used to write programs.

In this work, we restrict our attention to specifying *reactive systems* [PR89b, PR89a], or systems which continuously react to external stimuli. This is in contrast to *computational* programs which, given an input, produce some output and then terminate. Reactive systems are characterized by an infinite sequence of *environment inputs* and system *reactions*.

### **1.1** Synchronous Languages

We adopt the *synchrony hypothesis*, a notion first described in [BG92]. The hypothesis is best explained by the paper itself:

"Synchrony amounts to saying that the underlying execution machine takes no time to execute the operations involved in instruction sequencing, process handling, inter-process communication, and basic data handling."

The main purpose of adopting the synchrony hypothesis is to abstract away these details in order to focus on behaviors which are more relevant to the requirements set forth by the user. Requirements languages operating under this hypothesis are commonly referred to as *synchronous languages*.

The first synchronous languages were developed independently in the 1980s and early 1990s, most notably Esterel [BMR83], Lustre [HCRP91], Signal [GBGM91], and Argos [Mar90]. Prior to these languages, deterministic automata, Petri-Nets and concurrent programming languages were primarily used as requirements. None of the prior solutions were very succinct. Automata, for example, could easily grow beyond a size that is conducive to human understanding. Moreover, systems comprised of multiple components generally required asynchronous semantics, giving rise to other problems such as components "interrupting" each other during reactions.

The synchronous languages above are mostly text-based and exhibit the flavor of a programming language. They all have precise semantics, are relatively succinct, and abstract away irrelevant behavioral details.

### **1.2 Visual Modeling**

One drawback to the synchronous languages mentioned above is that they can sometimes be *too* succinct. A complete reactive system specification may appear to have a small amount of input, but at the cost of readability. For example, minor changes to the program input can dramatically change the output behaviors. Even worse, input changes may alter the output behaviors more subtly, in a way that eludes the designer. Therefore, larger more complex input programs can easily become unmanageable in practice.

An alternative approach is to describe behaviors *graphically* instead. Statecharts [Har87] is one such methodology which has enjoyed great commercial success. It exhibits the simplicity of finite state automata but addresses the size issue by injecting the notions of state-hierarchy, concurrency, and communication into the previously flat automaton model. A number of software tools have been developed to support Statecharts, most notably, Statemate [HLN<sup>+</sup>90] and Rhapsody [HG96, HK04].

#### **1.2.1** Message Sequence Charts

Another visual language is Message Sequence Charts. Originally standardized in 1992 [Z1293], Message Sequence Charts (MSCs) is a formal graphical requirements language originally used by the telecommunications industry for modeling the behaviors of distributed telecommunications software. MSCs were the original inspiration for *sequence diagrams* which were later adopted into the popular Unified Modeling Language (UML)[BRJ99].

MSCs offer an *inter-object* or *scenario-based* approach to behavioral modeling.

Rather than specifying the behavior of each object individually, MSCs model the interaction *between* objects. The individual object behavior is then inferred from the interaction.

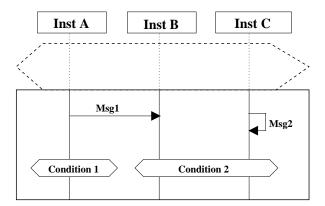

Each MSC scenario is depicted by a Basic Message Sequence Chart (bMSC), which visually depicts the participating *instances* in a scenario and the interactions between them. Under the synchrony hypothesis, atomic behaviors called *events* occur in zero time. The most basic form of interaction is the sending and receiving of asynchronous *messages* between objects over a reliable FIFO channel. Message sending and receiving are examples of events.

Each instance has a vertical *instance line*, representing a temporal top-to-bottom ordering of behaviors. Each instance line has an ordered set of *locations*, and there exists a surjective mapping from locations to events. The permissible ordering of events over one instance is a strict ordering of the locations on the instance line. The permissible ordering over multiple instances is a partial order over the locations. A bMSC *run* is a maximal linearization of the partial order.

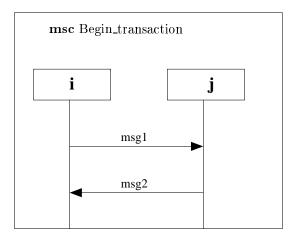

Figure 1.1: Basic Message Sequence Chart

Consider the MSC of Fig. 1.1, entitled Begin\_transaction. This scenario models the interaction between two instances, i and j. The horizontal arrows depict asynchronous *messages* sent from one instance to the other. According to this scenario, instance i sends message msg1, sometime after which instance j receives it. Another message, msg2 is communicated reciprocally.

MSC syntax can be converted into a textual BNF grammar, allowing one to reason formally about the structure. An extension of the original MSC standard [Z1293] provides a translation from the textual representation to a process algebra, which is intended to assign semantics to the language. The precision and scope of these semantics had been an issue of debate in the literature [LL93, Ren95]. Assuming a complete and unambiguous process algebra, the BNF grammar would imply the regularity of the MSC language in the sense that it can be converted into an automaton for the purpose of formal reasoning, such as verification.

#### **1.2.2 Multiple MSCs**

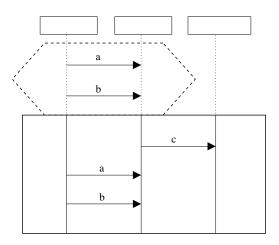

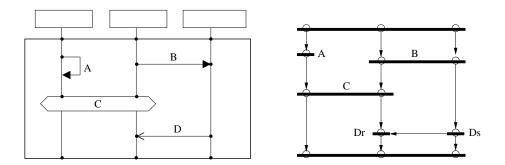

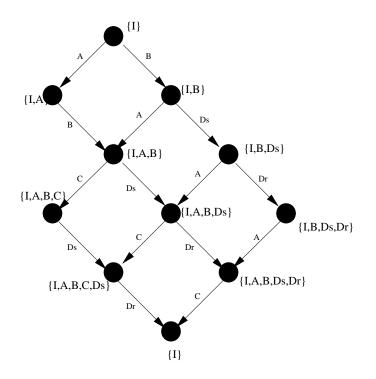

Most interesting systems are too complex to describe in a single bMSC. This gives rise to the question of how multiple MSCs can be combined to form complete requirements. This question is first addressed in the revised *MSC96* standard [Z1296], which offers two general solutions: The first proposes a flow graph called a High Level MSC (hMSC) that connects bMSCs using arrows. An hMSC may also contain other hMSCs, producing a hierarchical requirements structure. The second is *composition*, whereby continuation points located inside bMSCs depict the entry or exit points for other bMSCs. Fig. 1.2 illustrates the two methods.

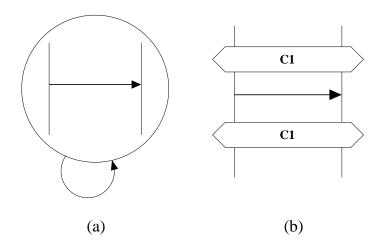

Figure 1.2: MSC Requirements using hMSCs and Sequential Composition.

High Level MSCs depict a flow of execution between vertices, each vertex denoting either a bMSC or another hMSC. An initial and terminal vertex is assumed. The vertices may connected—using branching choice, concatenation, and iteration—thereby inducing a language that expresses the entirety of the requirements. Fig. 1.2(a) shows a simple example of hMSCs using iteration.

The composition approach utilizes a condition, depicted by a hexagon, to denote the continuation of a scenario. For instance, when the bottom condition in Fig. 1.2(b) is reached, it synchronizes with the similarly labeled condition on the top, admitting an infinite execution.

#### 1.2.3 Shortfalls

The MSC example in Fig. 1.2(a) describes a non-regular language. Every send event must be paired with an eventual receive event and the FIFO queue can contain arbitrarily many send events, giving rise to the issue of unboundedness. This could occur,

for example, in a situation where messages have been sent but communication delays prevent them from being received right away.

Although a graphical means of specifying behavior could be useful for increasing readability, as we have just seen, MSCs unfortunately suffer from the same problems synchronous languages already addressed. In a sense, this is a step backward. Although problems such as the above have been addressed [HMNT99, HMKT00], the user is still forced to deal with these extraneous details.

Most software executes certain behaviors conditionally. It is therefore necessary on the requirements level to have a mechanism for specifying that certain behaviors are allowed or disallowed based on the truth values of conditions. The MSC standard suggests overloaded semantics for conditions. Conditions serve the dual purpose of restricting behaviors (*guarding conditions*) and making assertions over the state space (*setting conditions*). In the latter case, the condition may possibly double as a composition operator.

The process algebra suggested by the ITU standard unfortunately does not provide semantics for conditions in either case. Although variations have been suggested, none seem to have gained mainstream acceptance, making the absence of condition semantics a fairly significant drawback.

It has been argued in the literature that safety properties alone are insufficient for describing most reactive behavior. For example, Damm & Harel point out that MSCs lack *liveness*. That is, the ability to specify whether behaviors *can* happen or *must* happen. It is also unclear whether MSC conditions *can* or *must* evaluate to true. That is, whether false conditional evaluations are a violation of the requirements, or whether

they merely affect the subsequent behaviors.

### **1.3** Live Sequence Charts

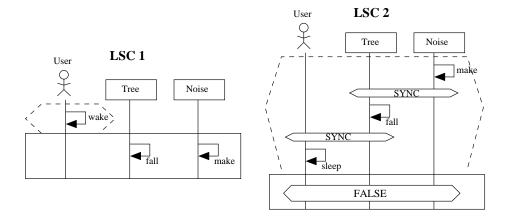

Live Sequence Charts (LSCs) [DH01] is an extension of MSCs which remedies the above shortcomings by adding liveness to the requirements, among other things. By assigning a hot or cold *temperature* to MSC messages, conditions, and locations, LSCs can describe whether events are mandatory or provisional. Additionally, they can describe whether or not scenarios themselves are mandatory, and if so, the conditions under which they must occur.

LSCs come in two varieties: *universal* and *existential*. Universal LSCs restrict the set of permissible behaviors by imposing requirements that must hold over all system runs. They can be used to describe scenarios that must happen and even *anti-scenarios*—those which must not happen. Existential LSCs, on the other hand, impose requirements which must hold over at least one system run. They can be viewed as the dual of universal LSCs: whereas universal LSCs *restrict* behaviors from occurring, existential LSCs *require* behaviors to occur.

Instances on an LSC are each identified by a name, which appear across top of the LSC within solid rectangles. Extending downward from these are *instance lines* which depict the flow of control for each instance in the scenario. Each instance executes the behaviors depicted on its instance line in a top-down manner. Universal charts consist of a *prechart*, annotated by a dashed hexagon, and a *main chart*, annotated by a solid rectangle. The relationship between the prechart and main chart is one of temporal

causality: if the behaviors of the prechart occur then the behaviors of the main chart are required to eventually occur.

LSC messages can depict a variety of real-life behaviors. For example, a message could represent a packet of transmitted data, the invocation of a function call, or a real-world event (e.g., sunrise). The type of event is usually understood by context. For our purposes, it is usually not necessary to make the distinction.

#### 1.3.1 Example

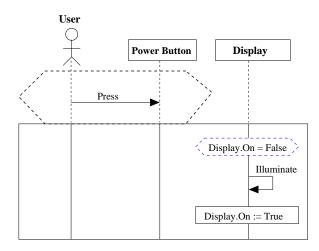

Consider Fig. 1.3, an example of LSC requirements consisting of precisely one scenario, described by a universal LSC. The scenario describes the requirements of a simple cellular phone power-on sequence. Three instances, User, Power Button and Display, participate in the scenario. Specifically, User represents the external environment and the other two instances belong to the cellular phone. In general, there can exist other scenarios belonging to the same requirements, which could describe additional behaviors over and above that of Fig. 1.3. For now, we focus our attention on single LSC requirements.

The prechart of Fig. 1.3 depicts a *synchronous message* called *Press* which is sent from User to Power Button. Synchronous messages, denoted by a solid arrow head, are characterized by the instantaneous occurrence of sending and receiving. In the example, User sends *Press* at the same instant as Power Button receives it. In real life, the message describes the act of physical touch—the sender and receiver of the message refer to the initiator and receipient of the action, respectively. An *asynchronous message*, not shown in this example, is depicted in the same way as synchronous mes-

Figure 1.3: Cellular Phone Scenario: Turn On

sages, except for an open arrowhead. Asynchronous messages are suitable for describing events in which a delay occurs between the sending and receiving.

LSCs may contain *LSC variables* and *object properties*, both of which are similar to variables in many imperative programming languages. They are both typed and refer to memory locations wherein discrete values, corresponding to the type, can be stored. LSC variables are an attribute of the LSC, whereas object properties are an attribute of an object. LSC variables are initially undefined each time the scenario begins executing, and are visible and mutable only within one particular LSC. In contrast, object properties are persistent between scenario executions and are visible to and mutable by any LSC in the requirements.

LSC variables and object properties can participate in LSC assignments and conditions. An assignment is depicted by a small solid rectangle and an embedded annotation of the form  $\varphi := x$  where  $\varphi$  is an LSC variable or object property and x is a constant. A condition is depicted as a small solid hexagon annotated by a predicate over the LSC variables and object properties. Based on the valuation of the variables or object properties, conditions evaluate to *true* or *false* in the obvious way.

When an LSC condition evaluates to true, the scenario proceeds beyond the condition. When it evaluates to false, the consequence depends on the *temperature* of the condition. Temperature is depicted by coloring the condition box red or blue, corresponding respectively to a *hot* or *cold* temperature. Hot conditions are *required* to evaluate to true—a false evaluation constitutes a violation of the requirements. A false evaluation of a cold condition, on the other hand, causes the scenario to terminate without violation<sup>1</sup>. The condition shown in Fig. 1.3 is cold, meaning that the scenario will proceed to the bottom of the main chart if the display is not on. Otherwise, the chart will terminate without violation. Intuitively, this means that the scenario is applicable only to the case where the display is not on.

Putting it all together, the scenario of Fig. 1.3 states that whenever the user presses the power button, it is required that either the Display must already be on, or otherwise must illuminate itself and then switch to an On state. This scenario handles only the case of the phone being turned on, even though the power button might serve as an on/off toggle.

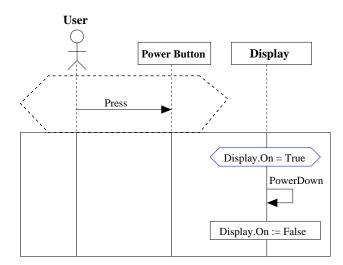

We expand the above requirements by adding the LSC of Fig. 1.4, which describes the scenario of turning off the phone. The LSC consists of a prechart which is identical to that of Fig. 1.3 and a main chart which is similar. The conditional expression at the top of Fig. 1.3 is the negation of the corresponding prechart in Fig. 1.3. Specifically, if the Display instance of Fig. 1.4 is in an On state, then it executes the *PowerDown* message and satisfies the main chart by setting the On variable to false. The LSCs

<sup>&</sup>lt;sup>1</sup>We assume in this work that LSCs do not contain subcharts. Generally speaking, however, if a cold condition within a subchart evaluates to false then only the subchart terminates.

Figure 1.4: Cellular Phone Scenario: Turn Off

of Figs. 1.3 and 1.4 work in conjunction with each other to describe the entire on/off switching behavior. When User sends the *Press* message, both precharts are simultaneously satisfied and the Display instance is then required to satisfy both main charts. If the phone's display is already off, then the "Phone Off" scenario in Fig. 1.4 immediately ends due to the condition. However, the "Phone On" scenario of Fig. 1.3 continues on to illuminate the display and then change the state of the display's On property to true.

#### **1.3.2** Justification for Use

The requirements phase of a software development life-cycle is arguably the most important, since it has been shown through practice that careful design reduces errors and overall implementation time. The requirements phase is intended to capture the behavioral description of the software. There is a vast range of requirements languages ranging from informal descriptions to rigorous and complete formal modeling tools. There exist contrasting viewpoints concerning the intended purpose of requirements, and the extent to which they should be used. Some practitioners view requirements as only an abstract description or set of general guidelines, rather than a concrete set of rules. According to this opinion, real-life requirements are too abstract and therefore insufficient for addressing the inherent complexities of a software system. Others adopt a stricter approach, citing that requirements should strive to express the most complete behavioral description possible, even if the state-of-the-art does not currently permit the level of rigor or formality necessary for a totally precise description. According to this point of view, an up-front reduction in the level of ambiguity results in a more guided development approach, thereby reducing the need for time-consuming discussions during the implementation phase.

This work is primarily directed to those who adopt the latter approach of utilizing formal and precise requirements languages to capture behavioral detail, or those willing to explore the possibilities of using this approach. We do not claim superiority of this approach over the former approach, or any other. However, we do maintain that the use of formal requirements languages have proven to be useful for a variety of reactive software projects.

In this work, we study the use of LSCs as a requirements language. Precise LSC definitions permit us to reason formally about LSC behavior for the purposes of synthesizing executable code. From a user standpoint, LSCs are related in appearance and function to UML sequence diagrams, with which many practitioners in the field are already familiar. We believe that a visual depiction of scenario-based behaviors is intuitive to not only professional developers, but also those with little or no technical background in software development. Existing tools such as the Play-Engine [HM03] also serve as

an aid in capturing LSC requirements by generating LSCs through the user manipulation of a graphical interface.

Although introduced only within the past few years, LSCs have already shown to be promising for developing or modeling many types of systems. For example, they have been used to model the weather synchronization logic for NASA's Center TRA-CON Automation System [BHK03], to create virtual wrappers for a PCI bus [BG02], to design a radio-based train system [BDK<sup>+</sup>02], and even to model living biological systems [KHK<sup>+</sup>03]. We find these initial results encouraging for developing the embedded software systems in which we're interested.

### **Chapter 2**

## **LSC Requirements**

We now provide definitions for the subset of LSC requirements considered in this work. The subset is comprised of messages, assignments, conditions, variables, and properties. These definitions are similar to the more extensive treatments appearing in [HK00a, HM03]. We begin with a discussion of untimed LSCs and then expand the discussion in Chapter 3 to include the notion of time. We focus initially on requirements consisting of only one LSC and then later treat the more common and expressive case of multiple LSC requirements.

#### 2.1 Object Systems

An *object system* is a set of objects which represent hardware, software, users, or other physical or conceptual entities that interact with one another. Each object acts on behalf of the *system* or *environment*. System objects are those belonging to and controlled by

the application we seek to design, whereas environment objects and their behaviors are outside the system's control.

#### 2.1.1 Definitions

Formally, an object system is a double  $Sys = \langle \mathcal{D}, \mathcal{O} \rangle$  where  $\mathcal{D}$  is a set of *application* types and  $\mathcal{O}$  is a set of *objects*. Each application type  $D \in \mathcal{D}$  is a finite set of values. We make a simplifying assumption that each set is strictly-ordered so that the binary comparison operators (e.g.  $\leq, <, \geq, >$ ) can be applied to all types. This allows us to develop a single theory, rather than addressing the formal details of a complete type system. For types where ordering doesn't make sense, the comparison operators aren't used.

An object is a triple  $\langle name, \mathcal{P}, own \rangle$  where name is the name of the object,  $\mathcal{P}$  is a set of properties (data members) and  $own \in \{sys, env\}$  classifies the object's ownership as either system or environment, respectively. Properties are defined by  $\langle name, D, \omega, \Theta \rangle$ , where name is the name of the property,  $D \in \mathcal{D}$  is its application type,  $\omega \in D$  is the property value, and  $\Theta$  is the initial value.

We adopt the convention of referring to elements of a tuple using an objectoriented "dot" notation. For example, to distinguish between the set of properties belonging to objects  $O_i$  and  $O_j$ , we write  $O_i \mathcal{P}$  and  $O_j \mathcal{P}$ , respectively. We also extend this notation to members of sets; for example, if we first establish the existence of a particular property  $p \in O_i \mathcal{P}$ , we may later write  $O_i p$  to make the ownership explicit.

The set of all properties is given by  $Props = \{p \mid p \in O.P \land O \in O\}$ . The state

space of the object system, denoted  $\Sigma[\mathcal{O}]$ , refers to the set of all valuations of properties in *Props*. The *initial valuation* of  $\Sigma[\mathcal{O}]$ , denoted *init*( $\Sigma[\mathcal{O}]$ ), is the valuation that maps all properties  $p \in Props$  to their initial value,  $p.\Theta$ .

#### 2.1.2 Relationship to LSCs

Intuitively, an object system can be viewed as the full set of components making up an executable program. Each component can communicate with other components by means of *messages*, which we refer to more abstractly as *behaviors*. Sending and receiving messages may cause the state of the objects (i.e., the property valuations) to change over time.

On a high level, LSCs model object system behaviors. They precisely describe acceptable and unacceptable behaviors. Given an object system and LSC requirements, we may check to see if any executable trace of that system agrees with the requirements. Alternatively, we may use the object system and requirements to automatically generate a "book of rules" by which the object system is guaranteed to agree with the requirements. The former method has already been implemented in a tool called the Play-Engine [HM03]. The latter method—also known as *synthesis*—is precisely the subject of this work, and we later describe an extension to the Play-Engine to support it.

## 2.2 Live Sequence Charts

Formally, a Universal Live Sequence Chart L over object system Sys is an 8-tuple defined by  $L = \langle I, M, V, A, C, Pch, evnts, temp \rangle$  consisting of:

- I a set of *instances*, each defined as a pair (locs, O) where locs is a (finite) totally ordered set of locations and O ∈ O is the object corresponding to the instance. We denote the set of locations of an instance i by locs(i). The location numbers across all instances are mutually distinct. We set locs(L) = U<sub>i∈I</sub> locs(i).

- M a set of messages (name, i<sub>s</sub>, i<sub>r</sub>, ℓ<sub>s</sub>, ℓ<sub>r</sub>, mode) where name is the name of the message, i<sub>s</sub>, i<sub>r</sub> ∈ I are the sending and receiving instances, ℓ<sub>s</sub> ∈ locs(i<sub>s</sub>), ℓ<sub>r</sub> ∈ locs(i<sub>r</sub>) are the locations at which the message is sent and received<sup>1</sup>, and mode ∈ {a, s} denotes whether the message is asynchronous or synchronous.

- V a finite set of typed LSC variables, each defined by (name, D, ω) where name is the variable name, D ∈ D is the type, and ω ∈ D ∪ {⊥} is the value. We use ⊥ to denote an undefined variable. We require all types D to be finite and discrete. By Σ[V] we denote the state space of V—that is, the set of valuations mapping each v ∈ V to a value v.ω. The *initial valuation* of V, denoted *init*(Σ[V]), is the valuation where all variables are undefined.

- A a set of assignments (locs, expr), where locs is the set of locations to which the assignment is anchored (i.e., visually attached to the location), and expr is an expression of the form "φ := x" where φ ∈ (V ∪ Props) and x ∈ φ.D. We denote the set of locations corresponding to a particular assignment a ∈ A by locs(a). If a is an assignment, we may refer to φ as a.φ and x as a.x.

- C a set of *conditions* (locs, expr), where locs is the set of locations to which the condition is anchored. Conditions compare either variables or properties to a

<sup>&</sup>lt;sup>1</sup>An instance may send a message to itself, in which case  $i_s = i_r$  and  $\ell_s = \ell_r$ .

constant using an operator  $\# \in \{=, <>, <, >, \leq, \geq, =, \neq\}$ . In particular, expression expr is of the form " $\varphi \# x$ " where  $x \in v.D$ .

- $Pch \subseteq locs(L)$  a prechart.

- evnts: locs(L) → E a many-to-one mapping between locations and events. The set of events, E consists of the union of visible events E<sub>v</sub>, hidden events E<sub>h</sub>, and unrestricted events E<sub>u</sub>. Events are discussed in greater detail in section 2.5. Let evnts<sup>-1</sup>: E → 2<sup>locs(L)</sup> map an event to the set of locations in the LSC where the it occurs.

- temp: locs(L) ∪ C → {H, C, W} maps a location to a hot, cold, or warm temperature. Also maps a condition to a hot or cold temperature. We turn to the topic of temperature in the next section.

## 2.3 Liveness

Each LSC instance depicts a visual top-to-bottom ordering of events, as represented formally by the instance's ordered set of locations. When an object system executes, each instance begins in its topmost location. During the course of execution, the LSC keeps track of the current location and moves to the next consecutive location whenever the event corresponding to that location occurs.

A central concept of LSCs is the notion of *liveness*, which is expressed by assigning a temperature to every location. The temperature of a location tells us whether the next consecutive event *can* or *must* occur. In the former case, the object system is given the choice of whether or not to execute the next event. In contrast, failure to ever execute it in the latter case is considered a violation of the requirements.

### 2.3.1 Hot and Cold Temperature

A cold location, depicted by a blue location coloring, represents that an instance may either remain forever at the location or progress. Hot locations, depicted by a red location coloring, impose a mandatory progress requirement. To avoid dependence on color displays, location temperatures in the following example and throughout the remainder of this work are depicted by the letters H, C, denoting hot and cold, respectively. Later we will discuss the *warm* temperature, which is depicted on the LSC by the letter W.

Later, in section 2.8.1, we formally discuss the concept of a *cut*, which is a snapshot of an LSC's configuration during execution. Roughly speaking, it is the product comprised of one location from every instance. Hot and cold temperatures extend to cuts in the following way. A *cold cut* consists of all cold locations, whereas a *hot cut* consists of at least one hot location. Similar to location temperatures, an LSC may remain forever in a cold cut without violating the requirements, whereas hot cuts require eventual progress.

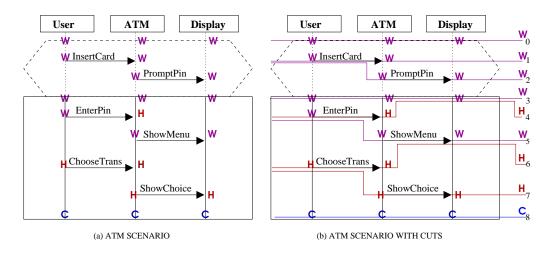

Consider the scenario of Fig. 2.1(a) which illustrates the interaction between a user (shown as User), automatic teller machine (ATM), and a user display (Display). Fig. 2.1(b) shows the cuts overlaid on Fig. 2.1(a). For the purposes of this example, we number the cuts  $0, \ldots, 8$  and show the temperature of each using letters H and C on the far right.

Figure 2.1: LSCs with Fairness

The LSC is in precisely one cut at a time, starting at cut 1 and progressing sequentially. Cuts 0, 3, and 8 are special cuts which are not associated with any messages, the first and last of which are the *initial* and *final* cut, respectively. In order to reach these cuts, special *hidden events* must occur. Hidden events are discussed in further detail in section 2.8.6.

Fig. 2.1 requires that whenever a user inserts a card (cut 1) and the ATM prompts the user for a PIN on the display (cut 2), the prechart is satisfied (cut 3) and the main chart is consequently required to eventually be satisfied. In particular, when User sends *EnterPin*, the main chart progresses to cut 4. Since cut 4 is hot, the ATM is required to send the *ShowMenu* to Display, causing the main chart to progress to cut 5. Since cut 5 is cold, no progress is required from this point. However, if User sends the *ChooseTrans* message, the LSC progresses to cut 6—a hot cut—from which it is required that ATM eventually send the *ShowChoice* message. When the message is sent, the LSC progresses to cut 7. The LSC can finally move to cut 8, thereby satisfying the LSC.

#### 2.3.2 More on Cold Temperatures

The LSC literature describes two possible interpretations of cold temperatures. According to the first, instances take the lazy approach of never progressing from a cold cut. This interpretation is safe in the sense that no harm can be done (with respect to violating the requirements) by remaining forever in a cold cut. We refer to this as a *minimal* policy, as defined in [HM03].

The second interpretation states that instances should always progress from a cold cut if they can, despite the absence of a requirement to do so. This option is not as safe because sometime after leaving the cold cut, the possibility of a future violation arises. This interpretation follows a *maximal* policy.

Precharts contain only cold locations by which follow a maximal policy. There would be no need for a main chart otherwise, since it would never be reached under a minimal policy. Main charts, on the other hand, can follow a minimal or maximal policy. The Play Engine, in particular, follows a maximal policy for both precharts and main charts.

#### **2.3.3** Warm Temperatures

Rather than assign two or more possible semantics to cold locations, we instead assign the minimal policy exclusively to cold temperatures and create a new *warm* temperature to express the maximal policy.

Aside from obtaining greater clarity, another advantage of this approach is that we permit the user to freely use cold, warm or hot temperatures within the main chart of universal LSCs. Whenever a sequence of one or more warm locations precedes a sequence of one or more hot locations, this is equivalent to stating that if all events leading up to the last warm location occur, then all the events associated with the subsequent hot locations must occur. For this reason, we require that all prechart locations are warm. A similar semantics is also suggested for Modal Sequence Diagrams in [HM07], whereby alternation between *cold fragments* (blocks of warm locations) and *hot fragments* (blocks of hot locations) is permitted.

We say that an event is *enabled* if it is legal for that event to occur next based on the sequence of events that has already occurred. We have already mentioned LSC cuts, which record the present position of each instance along an instance line, and hence the set of events which have already occurred. Therefore, we typically say that events are enabled or not enabled with respect to some cut. The notion of enablement is discussed more formally in section 2.8.2.

Cuts map to temperatures in the following way: if any location in the cut is hot, then the cut is hot. If no locations in the cut are hot, but at least one location is warm, then the cut is warm. Otherwise, the cut is cold. With these notions of cut temperature and enablement, we arrive at the following semantics for expressing LSC liveness properties:

- If an enabled event occurs from a warm cut, the LSC must progress from that cut.

- If a non-enabled event occurs from a warm cut, the LSC must remain forever in the warm cut.

We hereafter assume that all prechart locations are warm. Main chart locations may be either cold, warm, or hot, except for the locations appearing at the very bottom of the chart, which must be cold so that the chart closes. These assumptions do not affect the later results of this work, but are adopted only to remain consistent with the generally accepted LSC semantics.

If an LSC is in a warm cut and the next event causes a violation of the partial order, the LSC remains in the current cut forever. If the cut were cold, the decision to remain there forever would have been made upon reaching the cut. As described above, warm cuts permit the decision (of whether or not progress) to be delayed until the next event occurs. In either case, when the decision to remain forever in the cut has been determined, the LSC may close without violation since all obligations have been fulfilled. From a practical standpoint, it is wasteful to consume memory resources to perform bookkeeping for an LSC whose state will never change in the future.

We illustrate the use of warm locations using the example of Fig. 2.2. This example is identical to Fig. 2.1 except that certain cold locations have now been replaced by warm locations. In particular, we make all prechart locations warm and, additionally, change some of the main chart temperatures from cold to warm.

When message sequence *InsertCard*, *PromptPin* occurs, the LSC progresses to cut 3 thereby satisfying the prechart. Since cut 3 is warm, the LSC is required to progress if *EnterPin* occurs, but the main chart closes without violation if some other message occurs. Supposing that *EnterPin* occurs, the LSC advances to cut 4—a hot cut. It is therefore required that *ShowMenu* eventually occur. If it does, the LSC progresses to cut 5. Because cut 5 is warm, the LSC must progress if *ChooseTrans* occurs or the LSC otherwise closes without violation. Supposing *ChooseTrans* occurs, the LSC progresses to cut 6, from which there is a new requirement that *ShowChoice* must eventually occur.

If it never does, the requirements are violated. Otherwise, the LSC advances to cut 8—a cold cut—which causes the LSC to close.

Figure 2.2: LSC with Warm Temperatures

Fig. 2.2 illustrates classic reactive behavior, where User is viewed as the external environment and ATM, Display belong to the system whose behavior we are specifying. We see a series of obligations created during the course of the run. The requirements of this example essentially state that if the system and environment cooperate in producing the message sequence *InsertCard*, *PromptPin*, then the following holds: if the environment sends *EnterPin* then the system must eventually send *ShowMenu*. Thereafter, if the environment sends *ChooseTrans* then the system must eventually send the message *ShowChoice*.

The above example describes a set of "if-then" behavioral requirements. Without warm locations, the above behavior could not be described using only one LSC. Roughly speaking, each "if" would require a prechart of its own, and therefore a distinct LSC.

#### 2.3.4 Conditions

Conditions are depicted on LSCs as small hexagons with a dashed border. Inside the hexagon is a *conditional expression* over the LSC variables and object properties. When a specific valuation in  $\Sigma[V] \cup \Sigma[\mathcal{O}]$  is applied to the expression, a Boolean output is produced, indicating whether the expression is true or false. Conditions are treated more formally in section 2.8.3, but we provide a brief overview of the semantics here.

Conditions are *anchored* to locations on one or more instance lines. Instance lines that are attached to a particular condition are said to *participate* in that condition. When all participating instances are exactly one location above the condition, the condition can be *evaluated*. If the evaluation is true, all instances move onto the condition simultaneously. The outcome of a false conditional evaluation depends on the condition's *temperature*, which is determined by the *temp* function.

All conditions, similarly to locations, take on a hot or cold temperature<sup>2</sup>. Hot conditions are shown on the LSC by a red hexagonal border, whereas cold conditions are blue. We now explain the significance of condition temperature.

Each LSC scenario tells the story of a behavioral interaction among instances. The story begins with all instances at the topmost locations and ends when they arrive at the bottom. Sometimes its necessary to end the story prematurely, for example when the system is in a state from which it makes no sense to proceed. *Cold conditions* are used to abort scenarios in this way. When a cold condition evaluates to false, the LSC closes normally.

<sup>&</sup>lt;sup>2</sup>There are no warm conditions.

In other cases, a requirements designer may wish to assert that it is unacceptable for the system to arrive at or remain in a particular state. A system that reaches such a state is said to be in violation of the requirements. *Hot conditions* are used to perform the assertion. If the system remains in a state where a hot condition evaluates to false, this is considered a violation of the requirements.

# 2.4 Variables and Properties

Variables and properties are analogous to local method variables and data members in an object-oriented program. Both are finite discrete types, but they differ in lifetime and scope. *Lifetime* refers to the temporal duration in which a variable or property is available for use. A variable or property is *visible* if it can be legally referenced in a specific place in the requirements. *Scope* refers to the set of visible places.

Each LSC maintains a set of its own variables which are visible within the LSC. We assume that variables can appear only within assignments and conditions<sup>3</sup>. The lifetime of a variable begins when it is initialized to a value using an assignment and ends when the scenario terminates.

In contrast, properties are attributes of objects, not LSCs. An object's property is visible from any LSC in which the object appears. All properties have an infinite lifetime which commences at the start of execution. That is, the value of every property persists beyond the termination of any one scenario. One consequent of this setup is that property mutation in one LSC may alter the outcome of behaviors in another LSC

<sup>&</sup>lt;sup>3</sup>In the full LSC language, variables can be used as message parameters. If the same message appears in more than one LSC, unification is necessary to reconcile the variable bindings.

of the same requirements. Like variables, properties appear only in assignments and conditions.

In the full LSC definitions, variables can be assigned a constant value, the value of an object's property, or a user-supplied function. In this work, we assume that variables are assigned constant expressions only. This is a simplifying assumption only, as the other two cases could be handled similarly. The main requirement is that variables are assigned a value which is within their respective finite domain D. In the case of a user-supplied function, we further require the function to be defined for all inputs and range over any subset of D.

## 2.5 Events

Reactive systems produce behaviors that are visible to the outside world. LSCs observe these behaviors and update their state accordingly. Events serve as the connection between the behaviors of the reactive system and the LSC requirements. Events identify behaviors (e.g., a message name) and the objects participating in the behaviors (e.g., the sender and receiver). LSCs respond to events and map them to locations. A single event can map to one or more multiple locations. There are two possible reasons for the latter. The first is that several instances can participate in the same event—for example, instances synchronizing on a condition. The second is that the event needs to happen more than once during the scenario.

We proceed to define events in the following way. The set of LSC *events* is denoted by E, whose membership is comprised of the union of disjoint subsets  $E_v$  (visible

events),  $E_h$  (hidden events), and  $E_u$  (unrestricted events).

Visible events are observable behaviors, which are comprised of the sending and receiving of messages between objects. The set of visible events is given by  $E_v = E_v^1 \cup E_v^2 \cup E_v^3$ , where  $E_v^1, E_v^2, E_v^3$  are defined as follows. The set of synchronous message events is defined by  $E_v^1 = \{(m.name, m.i_s.O, m.i_r.O) \mid m \in M \land m.mode = s\}$ . That is, the name, sending object and receiving object for all synchronous messages. The sending and receiving are considered separate for asynchronous messages:  $E_v^2 = \{(m.name, m.i_s.O) \mid m \in M \land m.mode = a\}$  and  $E_v^3 = \{(m.name, m.i_r.O) \mid m \in M \land m.i_r.O\}$

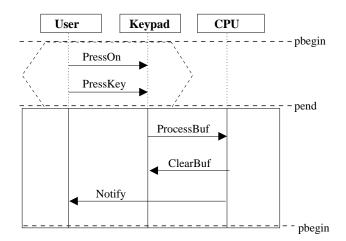

The set of hidden events is given by  $E_h = E_h^1 \cup E_h^2 \cup E_h^3$ , which are defined as follows. The set of hidden events is  $E_h^1 = \{pbegin, pend\}$ , referring to the synchronization of instances at the beginning and end of a prechart, respectively. For assignments, we have  $E_h^2 = \{a. \exp r \mid a \in A\}$  and for conditions,  $E_h^3 = \{c. \exp r \mid c \in C\}$ .

Unrestricted events with respect to an LSC are those which are irrelevant to the LSC scenario but may legally occur in any order<sup>4</sup> during its execution. This form of abstraction permits the user to focus on relevant behaviors while not necessarily excluding irrelevant ones. The set of unrestricted events,  $E_u$ , is specified a priori by the user and must satisfy  $E_u \cap E_h \cap E_v = \emptyset$ .

Function *evnts* maps locations to events and satisfies the following:

- Assignments:  $\forall a \in A \ \forall \ell, \ell' \in a. locs : evnts(\ell) = evnts(\ell')$

- Conditions:  $\forall c \in C \ \forall \ell, \ell' \in c.locs : evnts(\ell) = evnts(\ell')$

<sup>&</sup>lt;sup>4</sup>If there exist multiple LSCs in the requirements, the other LSCs could impose an ordering requirement.

• Synchronous Messages:

$$\forall m \in M : [m.\texttt{mode} = s] \Rightarrow evnts(m.\ell_s) = evnts(m.\ell_r)$$

The first two statements tell us that all locations of an assignment or condition correspond to the same event. The third statement says that the sending and receiving of a *synchronous* message refers to the same event. We also require:

• Prechart Initiation:

$$\forall \ell, \ell' \in \{\min(\mathsf{locs}(i) \cap Pch) \mid i \in I\} : evnts(\ell) = evnts(\ell') = pbegin$$

• Prechart Completion:

$$\forall \ell, \ell' \in \{\max(\texttt{locs}(i) \cap Pch) \mid i \in I\} : evnts(\ell) = evnts(\ell') = pend$$

• Main Chart Completion:

$$\forall \ell, \ell' \in \{\max(\texttt{locs}(i)) \mid i \in I\} : evnts(\ell) = evnts(\ell') = pbegin$$

We refer to the bulleted items above as *synchronizing* events, since their main function is to synchronize all instances at particular points during execution. Specifically, the first two items state that the instances synchronize at the top and bottom of the prechart. All locations at the top and bottom of the prechart refer to the events *pbegin* and *pend*, respectively. A similar synchronization occurs at the bottom-most locations of the main chart. Notice that the top-most locations of the prechart and bottom-most locations of the main chart both correspond to the same event, *pbegin*. Consequently, control returns to the prechart at the precise instant that the main chart scenario completed.

## 2.6 Temporal Event Ordering

We now establish a series of assertions characterizing the temporal order of events based on the constructs appearing on an LSC.

For LSC *L*, we write  $\ell_x^i$  to represent location *x* of instance *i*. Additionally, we write  $evnts(\ell_x^i) <_T evnts(\ell_y^i)$  to express that  $evnts(\ell_x^i)$  occurs strictly before  $evnts(\ell_y^i)$ . For some instances *i*, *j* and some  $x \in locs(i), y \in locs(j)$ , we write  $evnts(\ell_x^i) =_T evnts(\ell_y^j)$  to express that  $evnts(\ell_x^i)$  occurs at the same instant as  $evnts(\ell_y^j)$ . The temporal relation has a transitivity property which carries over to multiple instances in the sense that  $evnts(\ell_x^i) <_T evnts(\ell_y^i)$  and  $evnts(\ell_y^i) =_T evnts(\ell_x^j)$  implies  $evnts(\ell_x^i) <_T evnts(\ell_x^j)$ .

A simultaneous region is a maximal set of locations satisfying the temporal property "happens at the same time." More formally, a simultaneous region is a set of locations S such that there exists an event e where for all  $\ell \in S$  we have  $evnts(\ell) = e$ . Moreover, for all locations  $\ell' \in locs(L) \setminus S$ , we have  $evnts(\ell') \neq e$ . We denote by  $Sims_L$  the set of simultaneous regions of L.

## 2.7 Visible Events

Recall that visible events refer to the sending and receiving of messages. We impose the following requirements on visible events:

•

$$\forall m \in M : (m.mode = synchronous) \Rightarrow evnts(m.\ell_s) =_T evnts(m.\ell_r)$$

•  $\forall m \in M : (m.mode = asynchronous) \Rightarrow evnts(m.\ell_s) <_T evnts(m.\ell_r)$

The first requirement states that synchronous messages must be sent and received at the same instant. The second states that asynchronous message must be sent strictly before it is received.

# 2.8 The LSC Language

An LSC operates by continuously observing events and updating its state accordingly. We now define the notion of state more precisely.

#### 2.8.1 Cuts

A cut is a tuple consisting of:

- A valuation mapping every object property to a value.

- A valuation mapping every LSC variable to a value.

- A mapping from every instance to a location.

Formally, the set of cuts is given by:

$$Cuts = \Sigma[\mathcal{O}] \times \Sigma[V] \times \prod_{i \in I} locs(i)$$

For a cut  $\alpha$ , we write  $\Sigma[\mathcal{O}](\alpha)$  to represent a specific valuation which maps every property to some value. Similarly, we write  $\Sigma[V](\alpha)$  to represent the valuation mapping all LSC variables to a value in  $\alpha$ . Finally, we write  $\pi(\alpha)$  to represent the locations of the cut—an instance-to-location mapping—which due to the mutual distinction among locations, we express here for convenience as a *set* of locations. That is,  $\pi(\alpha) = \{\ell_1, \ldots, \ell_k\}$ , for some cut  $\alpha$  where k = |I|.

The *initial cut*, denoted  $init(\alpha)$ , is the cut  $\alpha$  where all instance locations are set to their top-most locations, all LSC variables are undefined ( $\alpha(v) = \bot$ , for all  $v \in V$ ), and all object properties map to some initial value ( $\alpha(p) = p.\Theta$ , for all  $p \in Props$ ).

The *temperature* of a cut  $\alpha$  is a function of  $\pi(\alpha)$ . Specifically,

- $temp(\alpha) = H \Leftrightarrow \exists \ell \in \pi(\alpha) : temp(\ell) = H$

- $temp(\alpha) = W \Leftrightarrow temp(\alpha) \neq H \land \exists \ell \in \pi(\alpha) : temp(\ell) = W$

- $temp(\alpha) = C \Leftrightarrow temp(\alpha) \neq H \land temp(\alpha) \neq W$

#### 2.8.2 Enablement

The *down-closure* of a cut  $\alpha$ , denoted  $\downarrow \alpha$  is the set of locations at and above the cut on the LSC. That is,  $\downarrow \alpha = \{\ell_x^i \mid \ell_x^i \in \alpha \Rightarrow \forall y \leq x, \ell_y^i \in \alpha\}$ . Conversely, the *top-line* of a set N, denoted  $\top N$  is given by  $\{\ell_x^i \mid \ell_x^i \in N \land \nexists \ell_y^i \in N \text{ s.t. } y > x\}$ .

An event *e* is *enabled* from cut  $\alpha$ , denoted *enabled*( $\alpha$ , *e*), iff there exists a simultaneous region *s* such that all of the following hold:

- 1.  $\forall \ell \in s : evnts(\ell) = e$

- 2.  $\forall \ell_j \in s : \ell_{j-1} \in \alpha$

3.

$$\forall m \in M : [m.mode = a \land m.\ell_r \in s] \Rightarrow m.\ell_s \in \downarrow \alpha$$

The first statement says that all locations of the simultaneous region refer to the same event *e*. The second statement requires that the cut be precisely one location above each of the locations of *s*. The third statement states, in the case of asynchronous messages, that the message must have been sent at or before cut  $\alpha$ . We can also state explicitly that  $\alpha'$  is the enabled cut with the 3-parameter assertion  $enabled(\alpha, \alpha', e)$ .

Enablement may also be expressed in terms of sim-regions. Let  $S \subseteq Sims_L$  and define  $locs(S) = \bigcup_{s \in S} locs(s)$ . Given some subset  $S \subseteq Sims_L$  and a simultaneous region s', we say that s' is enabled from S iff  $enabled(\top locs(S), \top (locs(S) \cup \{s'\}), g(s'))$ , written simenabled(S, s').

#### 2.8.3 Assignments and Conditions

An assignment  $a \in A$  consists of an expression expr of the form " $\varphi := x$ " where  $\varphi$ is an LSC variable or object property in  $V \cup Props$  and x is a constant. We denote the *valuation* of  $\varphi$  in cut  $\alpha$  by  $\alpha(\varphi)$ . We define an assertion over  $\Sigma[\mathcal{O}]$  and  $\Sigma[V]$ , which relates two cuts  $\alpha$  and  $\alpha'$  with respect to an assignment:

$$assign(\alpha, \alpha', \varphi, x) = [\alpha'(\varphi) = x] \land [\forall \varrho \neq \varphi : \alpha'(\varrho) = \alpha(\varrho)]$$

This states that  $\varphi = x$  in cut  $\alpha'$  and the valuation of all other variables is unchanged between cuts  $\alpha$  and  $\alpha'$ . Similarly, a condition  $c \in C$  consists of an expression expr of the form " $\varphi \# x$ " where  $\# \in \{=, \neq, <, >, \leq, \geq\}$ . We introduce predicate *eval* :  $C \times Cuts \mapsto \mathbb{B}$  which, for expressions of the form " $\varphi \# x$ ," is defined by:

$$eval(c,\alpha) = c.\varphi \in V \Rightarrow [\alpha(c.\varphi) \neq \bot \land \alpha(c.\varphi) \ c.\# \ c.x]$$

Conditions are assigned a hot or cold temperature according to the function *temp*. Semantically, when an LSC arrives on a cold condition which evaluates to false, the LSC closes without violation. If it evaluates to true, chart progress is permitted to continue. A hot condition must evaluate to true before the chart may progress further, otherwise the LSC remains at the hot condition and will violate the requirements if it never progresses. We require the following for the next section:

$$unch(\alpha, \alpha', \varphi) : \alpha(\varphi) = \alpha'(\varphi)$$

This states that the value of  $\varphi$  remains unchanged between cuts  $\alpha$  and  $\alpha'$ .

#### 2.8.4 Successor Cuts

Let  $\alpha, \alpha'$  be cuts and let  $\alpha_{\Delta} = \pi(\alpha') \setminus \pi(\alpha)$ . That is, the set of locations of cut  $\alpha'$  minus the locations of  $\alpha$ . Intuitively, this refers to the locations of the event that caused the cut to change. Transitions between cuts are defined by a total function  $Next : Cuts \times E \mapsto 2^{Cuts}$ . We say  $\alpha'$  is a *successor* of  $\alpha$  iff there exists *e* such that  $\alpha' = Next(\alpha, e)$ . This is the case whenever all of the following hold:

1. enabled  $(\alpha, \alpha', e) \lor init(\alpha')$

Event e is enabled from  $\alpha$ , or leads to the initial cut.

2.  $\forall a \in A : [\texttt{locs}(a) \subseteq \alpha_{\Delta}] \Rightarrow [assign(\alpha, \alpha', a.\varphi, a.x)]$

When arriving on a variable assignment,  $\alpha'$  will reflect the new value of variable or object property  $\varphi$ .

3.  $\forall \varphi \in (V \cup Props)$  :  $[[\forall a \in A : a. \varphi \neq \varphi \lor locs(a) \notin \alpha_{\Delta}] \land \neg init(\alpha') \Rightarrow unch(\alpha, \alpha', \varphi)]$

If not arriving on an assignment or returning to the initial state, all variable and property valuations remain unchanged.

4.  $\forall c \in C : [locs(c) \subseteq \alpha] \Rightarrow eval(\alpha, c) = true$

Advancing beyond a condition in the LSC requires that the condition evaluate to true.

5.  $[temp(\alpha') = C] \Leftrightarrow init(\alpha')$

Transitions into cold cuts lead into the initial state (cause the LSC to close).

- 6. ∀c ∈ C : [locs (c) ⊆ α ∧ temp(c) = C ∧ eval(α, c) = FALSE] ⇒ init(α')

Transitions into false cold conditions lead into the initial state (cause the LSC to close).

- 7.  $init(\alpha') \Rightarrow \forall v \in V : \alpha'(v) = \bot$

All LSC variables are undefined in the initial state.

## 2.8.5 Runs & Computations

An *LSC run* is an infinite sequence of cuts  $\pi = \alpha_1, \alpha_2, \ldots$ , satisfying:

•  $init(\alpha_1)$  (initiality)

•  $\forall i \exists e_i : \alpha_{i+1} \in Next(\alpha_i, e_i)$  (consecution)

Let  $Accept = \{ \alpha \mid temp(\alpha) \neq H \}$ . Let  $Inf(\pi)$  be the set of cuts occurring infinitely often in run  $\pi$ . An *LSC computation* is an LSC run also satisfying:  $Accept \cap$  $Inf(\pi) \neq \emptyset$ . An *event trace* is the sequence of events induced by a computation. The *LSC language* of an LSC is the set of all event traces. If  $\sigma = e_i, \ldots, e_k$  is a subsequence of an event trace, we write  $Next^*(\sigma)$  iff there exists a sequence of cuts  $\alpha_i, \ldots, \alpha_{k+1}$  such that  $\alpha_{j+1} = Next(\alpha_j, e_i)$  for all  $i \leq j \leq k$ .

#### 2.8.6 Hidden Events

We distinguish between event behaviors which are produced by the reactive system (i.e., messages) and those which are internal to the LSC (i.e., assignments, conditions, and synchronization points). Later, we will construct an automaton which monitors a sequence of visible behaviors and decides whether it satisfies or violates the LSC requirements. It is first necessary to establish a semantics that determines precisely how hidden events are to be carried out based solely on the occurrences of visible events. We present one particular interpretation which will be assumed for the purposes of our construction in Chapter 4.