# CoRReT: A Constraint Based Environment Rapid Prototyping Real Time Programs

#### Krishna V. Palem

Courant Institute of Mathematical Sciences, NYU

#### **Abstract**

significant portion of the potential growth in the computer industry. However, this growth opportunity is being hampered by a lack of adequate support via software development wheel at well-defined intervals of time; failure to do so will result in a systemic failure of the automobile must sense and react to the friction coefficient between the brake pads and the example, a program running in the microprocessor controlling an ABS system in a modern controlling applications ranging from automobiles and games, to video-pumps in the tools, to aid the easy, rapid and correct prototyping of embedded applications brakes. Referred to typically as embedded systems, these applications constitute a programs with special timing relationships between their constituent elements. For information highway. These applications are distinguished by the fact that they use The information revolution that we are in the midst of has led to the use of computers

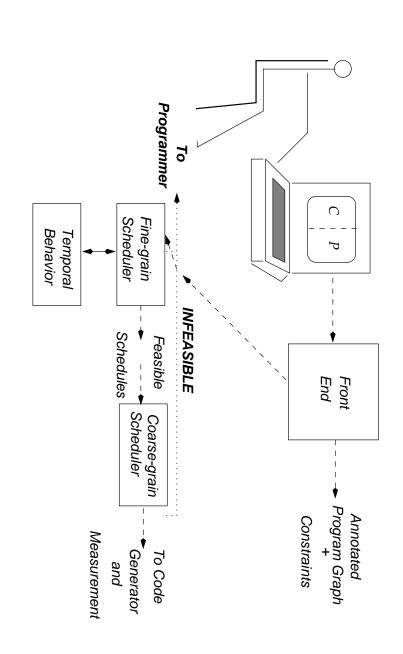

In this report, we outline CoRReT, a constraint based environment for the rapid well as the key modules in this environment that are being currently developed. CoRReT is prototyping of real time programs. The report outlines the overall system architecture as

\*Supported in part by an award from Hewlett-Packard Corporation, from IBM corporation, and a NYU research challenge grant.

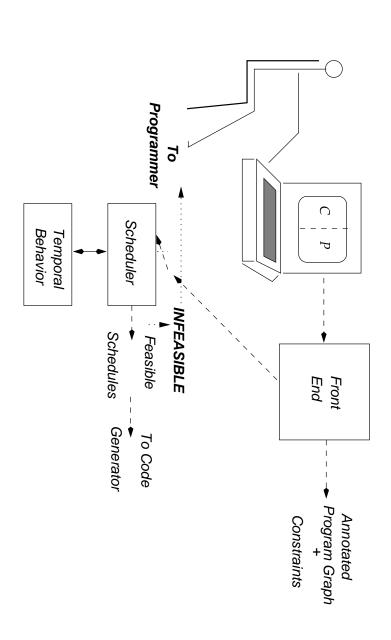

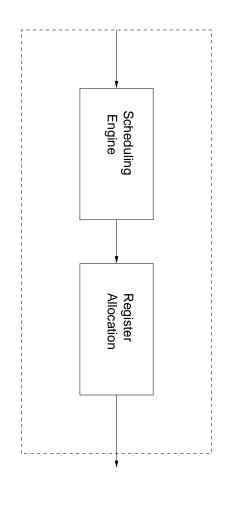

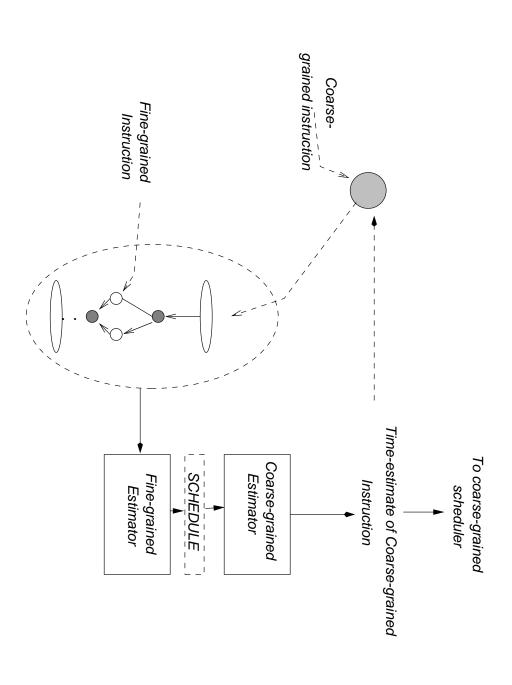

found, it will be fed automatically into a code-generator in the back-end of the compiler attempting to ensure that the timing constraints are met; when the constraints are met, a scheduling centric system in that a suite of algorithms for instruction scheduling programs by the programmer constraints in the source program — also cope with a variety of timing constraints specified the resulting schedule for the instructions is referred to be feasible. If a feasible schedule part of an (optimizing) compiler which will compile these programs automatically while instrumented with real-time constraints, are at its core. These algorithms are an integral Our envisioned scheduler can -- in addition to traditional control- and data-dependence S

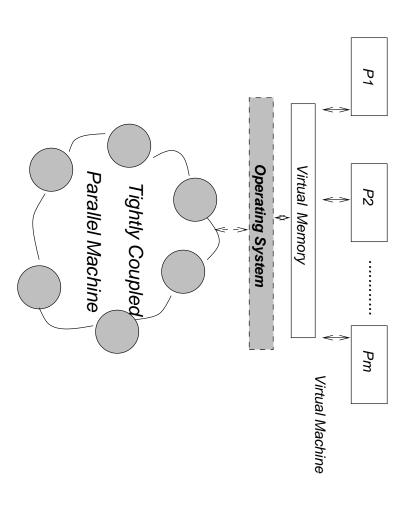

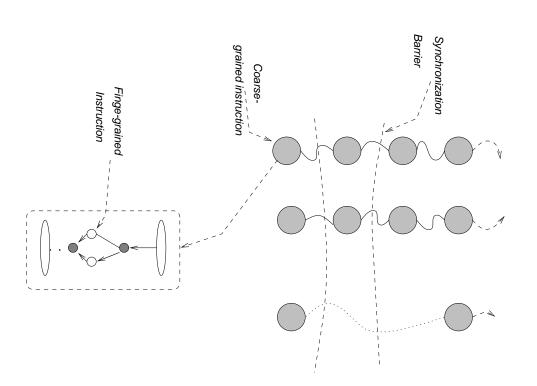

across the individual processors of the cluster. Furthermore, each processor in this parallel granularity. At the highest level, we envision a tightly-coupled parallel machine offering Our focus is on computational platforms that embody parallelism at two levels of machine can embody  $\mathit{I}$ nstruction  $\mathit{L}$ evel  $\mathit{P}$ arallelism ( $\mathit{ILP}$ ) at a fine-grained level. large-scale parallelism. In this setting, a single embedded application can be distributed

support through automation that frees the programmer of these difficulties, is a means of overcoming this challenge compounded by parallelism (at a fine-grained level) in the processor. Clearly, providing onerous task of ensuring timing relationships in the program by hand — a difficulty developers of embedded systems are reluctant to embrace ILP technologies due to the first, RISC processors with ILP have not yet found a niche in this domain; currently, computing platforms have not proliferated in this setting. Considering the fine-grained case compilation support for real-time constraints ubiquitous to embedded applications, parallel Unfortunately, due to a lack of automatic tools and technology that can provide

achieved in this direction at the coarse-grained level. The situation is even better at the context of embedded systems. In the absence of time-constraints, major progress has been tools for automatically harnessing very high performance from these platforms, in the compilers for RISC processors fine-grained level where scheduling technology is being used routinely in product-quality Our response to this challenge via CoRReT is to develop scheduling methodologies and

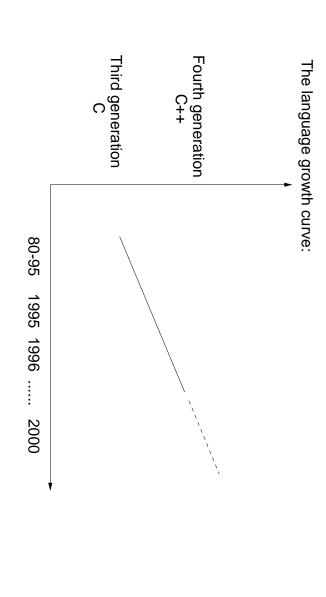

tools that go into CoRReT will naturally form an integral part of a full-fledged and the back-end of the compiler to generate code. We envision that the algorithms and aid in shorter prototyping cycles, since identical schedules will be used by the analysis tools programming environment for prototyping real-time programs on parallel platforms well as during compilation. We anticipate this "confluence" in the scheduling algorithms to processor, and is applicable to third and fourth generation languages. Furthermore, we propose to use the same scheduling engines during the static analysis of the program as The methodology on which CoRReT is based is independent of any particular target

### CoRRet: A CONSTRAINT Based Environment for Rapid Prototyping Real Time Programs

Krishna Palem

Courant Institute of Mathematical Sciences

# Target Domains for Real-time Applications

1. Hard Real-Time: Avionics, medical life-support, ...

Soft Real-Time: Entertainment (set-top boxes, games), utilities (microwaves, wrist-watches), ...

### **Building These Systems**

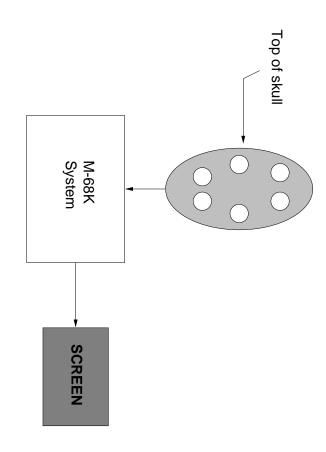

An example from my experience for real time processing of Electroencephalographic data in a doctor's office

- Data is arriving at about 10 KHz.

- Processor clocking about 10 MHz.

- the neuro-physician. Functions included data acquisition, analysis and real-time display to

### The High Level Approach

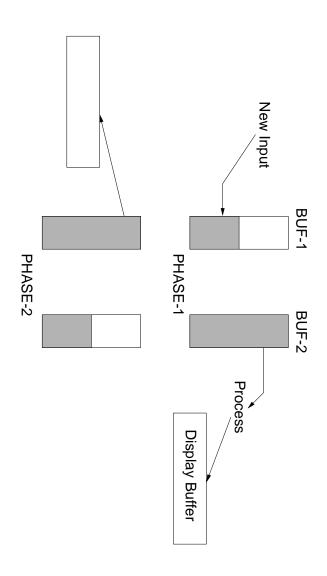

- Collect data in one buffer.

- Process in the other.

- When one of the buffers is full, switch input buffer and processing buffer.

## Some Simple Time-constraints

- every 0.1 m-sec. Processing software has to move ahead by one data point

- The switching of buffers has to occur in the same interval.

#### The Difficulty

- All the coding for the signal-processing had to be done in assembly.

- Had to "hand-tune" it to fit the constraints stated above.

- for displaying Other constraints involved interrupts from the board (8-bit) microprocessor to transfer the processed data over updating the display which was running a dedicated M6800

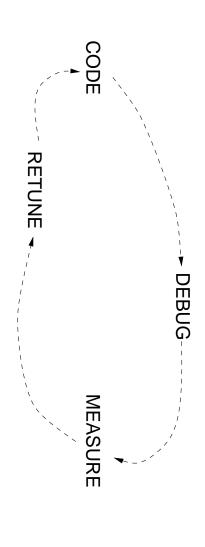

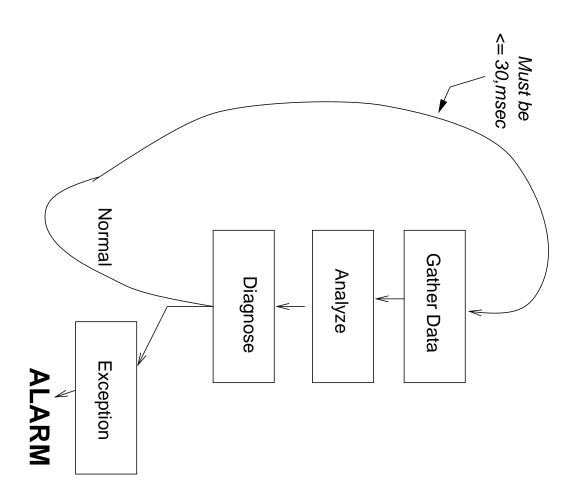

# Real-time Software Development in Industry

- Programmers spend a lot of time designing pieces of code.

- Estimate timing behavior via

- synthetic analysis, possibly with some tools, and

- executed actual measurement where code is produced and

- If timing "expectations" met, programs are returned till feasible. — informally specified are not

## Spurred by the RISC Processor Revolution

### Opportunity in Superscalars

- High degree of Instruction Level Parallelism (ILP) via to harness promised performance multiple Functional Units (FUs), each pipelined: Essential

- Clean simple model and Instruction Set makes compile time optimizations feasible

- automatically. Therefore, performance advantages can be harnessed

## Superscalar (RISC) Processors

| Register Bank | Pipelined Functional Unit e.g. Floating Point, Fixed-Point, Branch Predication, etc. |

|---------------|--------------------------------------------------------------------------------------|

#### Canonical Instruction set

- Load and store to/from memory (multiple cycles).

- Register-Register Instructions (single cycle). A few notable exceptions of course.

Eg., IBM Power & RS6K, DEC Alpha, Sun Sparc.

# Example Of Instruction Level Parallelism

#### Processor has

- 5 functional units: 2 fixed point units, 2 floating point units and 1 branch unit.

- are 1 deep. Pipeline depth: floating point unit is 3 deep, and the others

instructions being processed simultaneously. At peak rates, with a 71.5 MHz clock, 357.5 MIPs with 9

## Returning To Real-Time Computing

The technological trend enabling new applications:

- Rapid evolution of processor technology in terms of pertormance.

- Substantially lower \$\$ per MIPs.

- Makes much more ambitious real-time applications feasible.

- microprocessors— *Video-pumps* in the *information highway*. Hand-held games with 32-bit (embedded)

#### The Overall Challenge

- Error-prone and tedious as the complexity of the system grows

- the scale grows. Hence substantially superlinear growth in software development cost as

- potential. Limits the scale of the explosion and does not harness hardware

- Further compounded by the need to schedule instructions in the context of modern processors with ILP.

#### An Important Gap

#### Currently

Even with some automatic support.

Methods and algorithms used in analysis are not related to those aimed at compilation.

large. Gap between prediction and compiled code's feasibility is

Leads to long prototyping cycles.

#### The "Big Picture"

#### The Platform

## Our Envisioned Response

## The Proposed Environment

### In Thinking of Solutions

- Programmers are slow to migrate away from their favorite and stable languages.

- Radical proposals will not succeed.

- automatic support. Think of technologies that enhance existing languages in providing

- Consequently, we do not propose a new language.

#### The Technology

#### Provide Support for

- the program. Easily expressing "timing-relationships" between parts of

- Analyze the program to determine feasibility on the target platform.

- Generate code automatically if feasible.

### The Programming Model

## The Proposed Expressive Framework

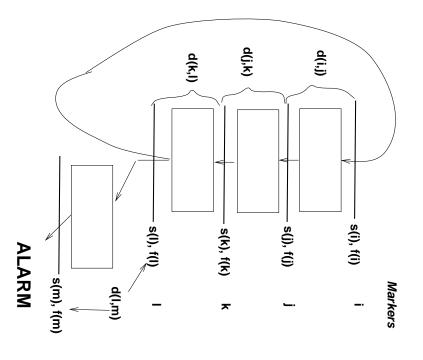

- Enhance the user program with zero-time executable markers shown by thick lines.

- Write timing relationships between markers are a distinct constraint system.

### The Timing Relationship

associated with markers as shown, example design specifications  $-\!-\!-$  all Given that **s**, **f** and **d** respectively denote the start, finish and the durations integers are m-sec — might be

1.

$$d(i,j) + d(j,k) + d(k,l) \le 20$$

2.

$$d(l,m) = 50$$

3.

$$f(l) - s(i) \le 100$$

#### A Simple Example

#### Cardiac Arrhythmia Detector

## Constraints As Time Specifications

Abstract representations.

specifications are decoupled from program's control flow and syntax.

Clean and minimal mechanism for expressing relationships.

Integer-linear constraints are rich in their expressive power.

compilation and analysis cost, Typically, abstract representations — Expensive

#### Feasibility via Analysis

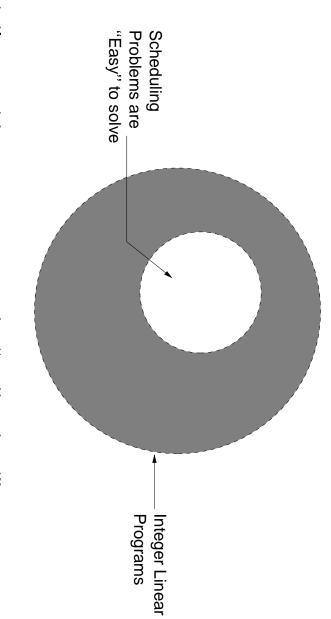

Constraint Satisfaction.

In general, satisfiability of Integer Linear Programs — A hard problem.

A key observations makes the difference.

# All the Integer Linear Programs are Scheduling Problem!

## More on Classical Scheduling

- Scheduling problems are extremely "well-solved".

- Fast algorithms produce very good solutions.

- Productions codes in industry run very well.

#### The Scheduling Model

In a program dependence graph representation

- constraints". Data- and control-dependences encode "precedence

- Instructions are the nodes.

- edges Pipelines delays on the target processor are latencies on the

- specified. A number and types of processor in the target processor are

## Traditional Well-solved Settings

- Acyclic control-flow structures.

- The goal is to minimize

- completion time to improve performance of code on the RISC processor,

- absolute deadlines to model limited form of hard real-time applications.

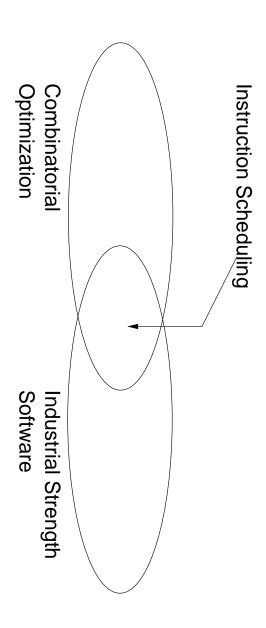

## The Core Research Question

problem with Reduced to solving a Precedence-constrained Scheduling

cycles in the graph,

absolute variants that have been addressed relative deadlines and start-times. As opposed to the

combinatorial optimization question. The entire problem is thereby reduced to a well-defined

### Significance of Reduction

- A single well-parameterized combinatorial optimization question captures the essence of:

- Analysis and

- Code generation (to be seen)

- Amenable to

- Powerful technical methods and

- Software engineering approaches

#### The Plug

- Same scheduling engine for code generation (as for analysis).

- Corresponds to a closer relationship between the analysis and the code generation phases

- Hence, the feasibility of compiled code is only and intimately dependent on the quality of the library describing the objects

- Very good libraries are available in the field very small gap between the two phases — tight design cycles.

#### The Bonus

In addition to aiding in the rapid-prototyping of real-time software, we are enabling the proliferation of RISC processors in the embedded system market.

## **Estimating Execution Times**

#### Milestones

(Done) **Prototyping Framework and Scheduling Engine Definition**

Fine-grained Scheduling Algorithm Design and Evaluation

into Compiler, validate and Develop GUI (with N. Nachiappan) **Develop Constraints Front-end and** Integrate Scheduing Engine