## Flexible and Efficient Systems for Training Emerging Deep Neural Networks

by

Minjie Wang

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Computer Science Courant Institute of Mathematical Sciences New York University January, 2020

Professor Jinyang Li

© Minjie Wang All Rights Reserved, 2020

# Dedication

To my beloved Naonao

# Acknowledgements

I am very thankful to work with my advisor Jinyang in this thrilling decade of deep learning explosion. As a quite demanding student, I constantly have a lot of questions or doubts, about research or others, and the most often response I hear from Jinyang is *"Sure, let's chat."*. Her sharpness and enthusiasm in her work is truly inspiring and is something I hope I could replicate.

I am indebted to ZZ, who has always put his trust in me via numerous projects, granting me the chances to freely explore the research wild, leading me out of swamps and pushing me to enjoy most of the applause. As a system research veteran, ZZ makes his decisive shift to embrace machine learning, an intrepid move that teaches me an ever-lasting lesson – it is always day one. ZZ's insightful perspective often amazes me in one and yet another projects; some failed but none of them missed.

I am also thankful to Chien-chin Huang, with whom I co-authored the Tofu system (Chapter 3) in this dissertation, for his dedication to this work at the time he just became a father. I will always remember the image that he skillfully launched a hundred instances with a baby in his arm. My committee members, Kyunghyung cho, Joan Bruna and He He, offered me precious advises and supports on my projects and thesis, which I really appreciate. I thank Yann Lecun, who helped my fellowship recommendation, and Sebastian Angel, who polished my application and also my coffee taste.

I feel grateful to Tianqi Chen and Mu Li, who brought me into open source community, and who have served as fantastic mentors, for their open attitude to collaboration and genuine open source spirit that inspired the DGL project (Chapter 4). I thank Tianjun Xiao, Yutian Li, Haoran Wang, Larry Tang, Yu Gai, Ziheng Jiang, Sean Welleck, with whom I co-worked on the Minerva and MinPy projects. My co-authors and co-workers, Lingfan Yu, Quan Qan, Jake Zhao, Zihao Ye, Mufei Li, Jinjing Zhou, Qi Huang, Da Zheng, Haibin Lin, Chao Ma, Damon Deng, Qipeng Guo, Hao Zhang, Ziyue Huang, made significant contributions to the design and implementation of DGL and I am grateful for their help.

I thank Lakshmi Subramanian and Mike Walfish for the advises and encouragement on my work and presentations. To all my friends at NYU, Cheng Tan, Shuai Mu, Zhaoguo Wang, Changgeng Zhao, Shiva Iyer, Christopher Michell, Ye Ji, Yan Shvartzshnaider, thank you for making the lab feel like a home. I thank Andy and Pat Wang for providing a wonderful homestay during my dissertation writing. Finally, I thank my family for their love and support.

## Abstract

The success of deep neural networks (DNNs) is due to its strong capability to learn from data. To continue such success, DNNs must handle the ever-increasing size and complexity of data. Two concrete challenges stand out. One, to leverage more data, one needs to train a large DNN model, the size of which becomes limited by the memory capacity of a single GPU. The other, to leverage graph structured data, one needs to use DNN models that perform sparse numerical computation. Unfortunately, current deep learning systems do not provide adequate support for very large or sparse models. This thesis develops two systems, Tofu and DGL, to enable efficient training of these emerging DNNs while minimizing user programming efforts.

Tofu supports very large DNNs by partitioning the computation across multiple GPUs to reduce per-GPU memory footprint. To automatically partition each operator, we propose a description language for annotating the semantics of an operator. To optimally partition the whole training, Tofu proposes an algorithm that minimizes the total communication cost. We evaluate and assess the capability of Tofu to train very models demonstrating the substantial gains by applying the design.

DGL is a new framework for training DNNs for graph structured data. DGL provides an intuitive and expressive message-passing interface that can cover a wide range of graph DNN models. We introduce batching and kernel fusion techniques that enable training GNNs on large graphs and achieve significant improvements in performance relative to existing systems.

# Table of contents

| D              | edica | tion                                                           | iii  |

|----------------|-------|----------------------------------------------------------------|------|

| A              | cknov | wledgements                                                    | iv   |

| $\mathbf{A}$   | bstra | $\mathbf{ct}$                                                  | vi   |

| $\mathbf{Li}$  | st of | Figures                                                        | x    |

| Li             | st of | Tables                                                         | xiii |

| 1 Introduction |       | oduction                                                       | 1    |

|                | 1.1   | Challenges with existing DL systems                            | 4    |

|                | 1.2   | Contributions                                                  | 6    |

|                | 1.3   | Roadmap                                                        | 9    |

| <b>2</b>       | Rela  | ated Work                                                      | 10   |

|                | 2.1   | Deep Learning Systems                                          | 10   |

|                | 2.2   | Parallel DNN Training                                          | 13   |

| 3              | Tof   | u: Supporting Very Large Models using Automatic Dataflow Graph |      |

| Partitioning   |       |                                                                | 15   |

|                | 3.1   | Introduction                                                   | 15   |

|                | 3.2   | Problem settings                                               | 18   |

|   | 3.3 | Challe | enges and our approach                                   | 20   |

|---|-----|--------|----------------------------------------------------------|------|

|   |     | 3.3.1  | How to partition a single operator?                      | 20   |

|   |     | 3.3.2  | How to optimize partitioning for a graph?                | 22   |

|   | 3.4 | Partit | ioning a single operator                                 | 23   |

|   |     | 3.4.1  | Describing an operator                                   | 23   |

|   |     | 3.4.2  | Analyzing TDL Descriptions                               | 25   |

|   | 3.5 | Partit | ioning the dataflow graph                                | 28   |

|   |     | 3.5.1  | Graph coarsening                                         | 29   |

|   |     | 3.5.2  | Recursive partitioning                                   | 31   |

|   | 3.6 | Optim  | nizations in generating the partitioned graph            | 34   |

|   | 3.7 | Evalua | ation                                                    | 36   |

|   |     | 3.7.1  | Experimental setup                                       | 37   |

|   |     | 3.7.2  | Training Large and Deep Models                           | 39   |

|   |     | 3.7.3  | Comparing different partition algorithms                 | 42   |

|   |     | 3.7.4  | Partition Results                                        | 45   |

|   | 3.8 | Additi | ional Related Work                                       | 46   |

|   | 3.9 | Conclu | usion                                                    | 48   |

| 4 | Dee |        | ph Library: An Efficient and Scalable Framework for Deep |      |

| 4 |     | -      | on Graph                                                 | 49   |

|   | 4.1 | U      | luction                                                  |      |

|   | 4.2 |        | round                                                    |      |

|   | 4.3 | 0      | n Challenges for DNNs on Graphs                          |      |

|   | 4.4 | v      | n Overview                                               |      |

|   | 4.5 | 0      | amming Interface                                         |      |

|   | 4.0 | 4.5.1  | Graph and feature storage                                |      |

|   |     | 4.5.2  | Message passing interface                                |      |

|   | 4.6 |        |                                                          |      |

|   | 4.0 | Optim  | nization and Implementation                              | - 59 |

|                                                                   |                 | 4.6.1   | Auto-batching user-defined message passing | 59 |

|-------------------------------------------------------------------|-----------------|---------|--------------------------------------------|----|

|                                                                   |                 | 4.6.2   | Fusing message and reduce functions        | 60 |

|                                                                   | 4.7             | Evalua  | ation                                      | 61 |

|                                                                   |                 | 4.7.1   | Speed and memory efficiency                | 62 |

|                                                                   |                 | 4.7.2   | Scalability                                | 62 |

|                                                                   |                 | 4.7.3   | Auto-batching                              | 65 |

|                                                                   | 4.8             | Conclu  | sion                                       | 65 |

| <b>5</b>                                                          | Con             | clusior | and Future Work                            | 67 |

|                                                                   | 5.1             | More (  | General Operator Specification             | 68 |

|                                                                   | 5.2             | More 1  | Extensive System Optimizations             | 69 |

|                                                                   | 5.3             | Scale t | to Real World Graphs                       | 70 |

| Appendix A Recursive Partitioning Algorithm and its Correctness 7 |                 |         |                                            |    |

|                                                                   | A.1             | Recurs  | sive partition plan                        | 71 |

|                                                                   | A.2             | Region  | ı Analysis                                 | 72 |

|                                                                   | A.3             | Comm    | unication cost                             | 73 |

|                                                                   | A.4             | Optim   | iality proof                               | 75 |

| Bi                                                                | Bibliography 76 |         |                                            |    |

# List of Figures

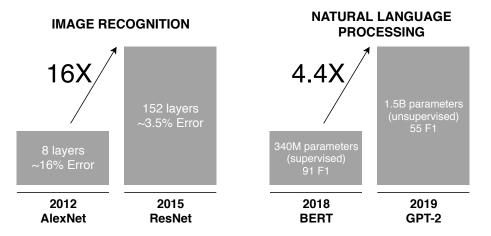

| 1.1 | The growth of DNN model size                                                               | 2  |

|-----|--------------------------------------------------------------------------------------------|----|

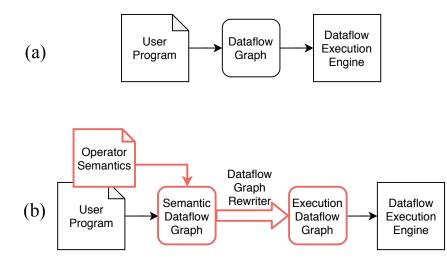

| 1.2 | (a) Current DL system design. (b) SMEX system design                                       | 3  |

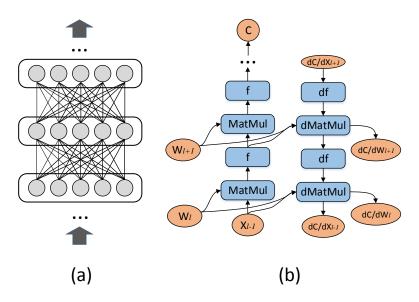

| 2.1 | (a) A Multi-Layer Perceptron (MLP) model; (b) The dataflow graph for its                   |    |

|     | forward and backward propagations.                                                         | 11 |

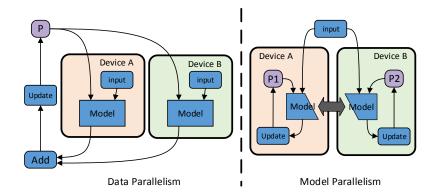

| 2.2 | Data parallelism and model parallelism                                                     | 13 |

| 3.1 | The naive implementation of conv1d in Python.                                              | 19 |

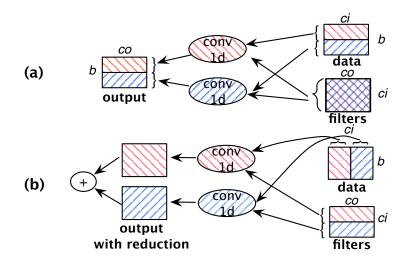

| 3.2 | Two of several ways to parallelize $\texttt{conv1d}$ according to partition-n-reduce. Each |    |

|     | 3D tensor is represented as a 2D matrix of vectors. Different stripe patterns              |    |

|     | show the input tensor regions required by different workers                                | 21 |

| 3.3 | Example TDL descriptions.                                                                  | 23 |

| 3.4 | Tofu's symbolic interval arithmetic                                                        | 27 |

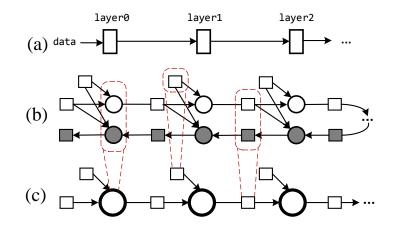

| 3.5 | (a) Layer graph of a MLP model. (b) Its dataflow graph including forward and               |    |

|     | backward computation (in grey). (c) Coarsened graph. For cleanness, we only                |    |

|     | illustrate one operator group, one group for activation tensors and one group              |    |

|     | for weight tensor (dashed lines).                                                          | 29 |

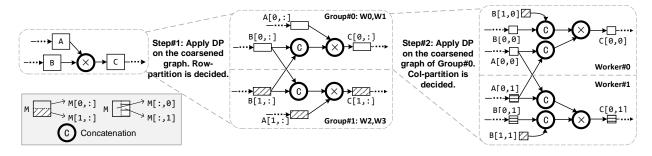

| 3.6  | Recursively partition a dataflow graph to four workers. Only one matrix mul-                                   |    |

|------|----------------------------------------------------------------------------------------------------------------|----|

|      | tiplication is drawn for cleanness. In step $\#1$ , every matrix is partitioned by                             |    |

|      | row, and for group#0, B[1,:] is fetched from the other group. Because of this,                                 |    |

|      | B[1,:] becomes an extra input in step#2 when the graph is further partitioned                                  |    |

|      | to two workers. Because step $\#2$ decides to partition every matrix by column,                                |    |

|      | every matrix is partitioned into a 2x2 grid, with each worker computes one block.                              | 31 |

| 3.7  | (a) Original dataflow graph; (b) Partitioned graph with extra control depen-                                   |    |

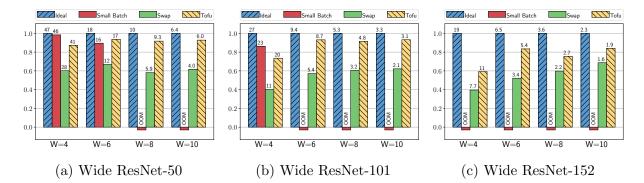

|      | dencies (dashed lines).                                                                                        | 34 |

| 3.8  | Normalized WResNet throughput relative to the ideal performance. The num-                                      |    |

|      | ber on each bar shows the absolute throughput in samples/sec. $\ldots$ . $\ldots$ .                            | 36 |

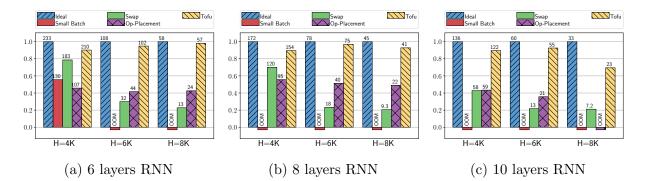

| 3.9  | Normalized RNN throughput relative to the ideal performance. The number                                        |    |

|      | on each bar shows the absolute throughput in samples/sec. $\hdots$                                             | 40 |

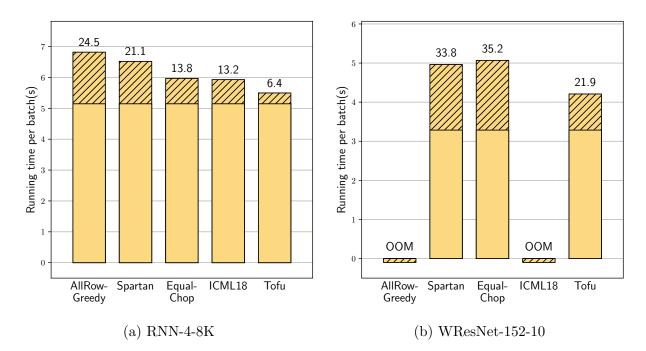

| 3.10 | Comparison of different partition algorithms using RNN-4-8K and WResNet-                                       |    |

|      | 152-10 on 8 GPUs. Striped parts show the overhead (percentage) due to com-                                     |    |

|      | munication.                                                                                                    | 43 |

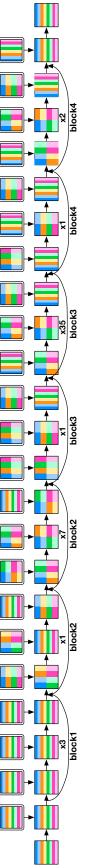

| 3.11 | The partition found by Tofu for WResNet-152-10 on 8 GPUs. We draw the                                          |    |

|      | weight tensors (top row) and the activation/data tensors (bottom row) used by $% \left( \frac{1}{2}\right) =0$ |    |

|      | convolution operators. Partitioning is marked by the tiles and each color shows                                |    |

|      | the tiles owned by the same GPU. The vertical and horizontal dimensions of                                     |    |

|      | an activation tensor indicate the batch and channel dimensions. 'xN' symbol                                    |    |

|      | means the corresponding block is repeated N times                                                              | 44 |

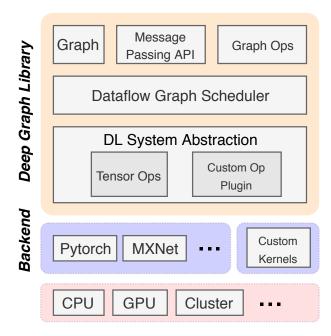

| 4.1  | DGL system stack.                                                                                              | 55 |

| 4.2  | Example codes of Graph Convolution layer in DGL                                                                | 56 |

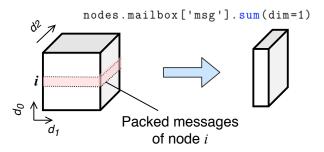

| 4.3  | The semantics of the message tensor dimensions in a reduce UDF                                                 | 59 |

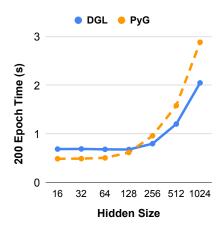

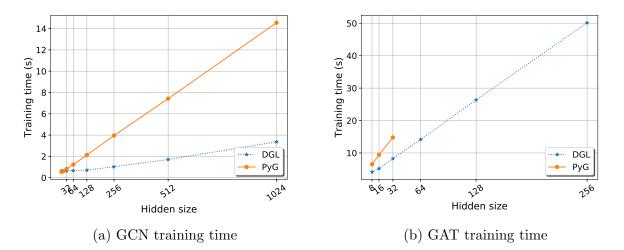

| 4.4  | GCN training time on Pubmed with varying hidden size.                                                          | 61 |

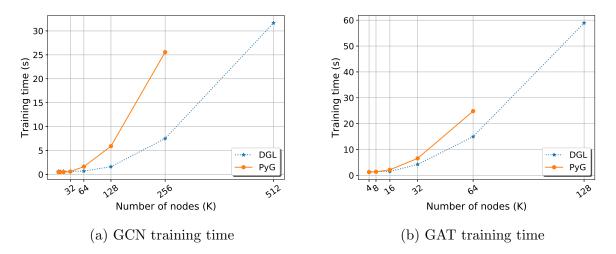

| 4.5  | Time to train GCN and GAT for 200 epochs on synthetic graphs of increasing                                     |    |

|      | number of nodes. All graphs have fixed density 0.08%                                                           | 63 |

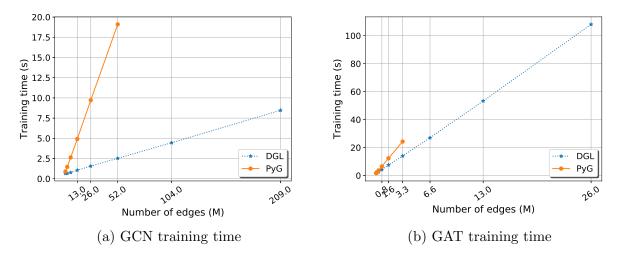

| 4.6 | Time to train GCN and GAT for 200 epochs on synthetic graphs of increasing  |    |

|-----|-----------------------------------------------------------------------------|----|

|     | density. All graphs have 32K nodes                                          | 63 |

| 4.7 | Time to train GCN and GAT for 200 epochs with increasing hidden sizes on a  |    |

|     | synthetic graph. The graph has 32K nodes and density is $0.08\%$            | 64 |

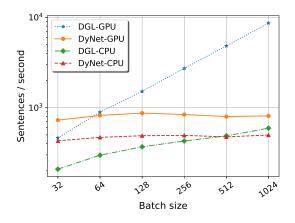

| 4.8 | Comparison of training throughputs between DGL and DyNet with auto-batching |    |

|     | on TreeLSTMs                                                                | 65 |

# List of Tables

| 3.1 | Time to search for the best partition for 8 workers. WRestNet-152 and RNN-10 $$  |    |

|-----|----------------------------------------------------------------------------------|----|

|     | are two large DNN models described in §3.7.                                      | 31 |

| 3.2 | Total weight tensor sizes (GB) of our benchmarks                                 | 37 |

| 3.3 | Comparison of throughput (samples/second) for RNN models. The hidden size        |    |

|     | is 4096                                                                          | 42 |

| 4.1 | DGL vs. GraphNet (GNet), NGra, Euler and Pytorch Geometric (PyG) $\ . \ . \ .$   | 52 |

| 4.2 | Training time (in seconds) for 200 epochs and memory consumption (GB). $\ . \ .$ | 61 |

# Chapter 1

# Introduction

Recent years have seen tremendous success of deep learning. The resurgence of *Deep Neural Networks* (DNNs) have caused major paradigm shifts with substantial breakthroughs [1, 2, 3, 4, 5, 6]. The success of *Deep Learning* (DL) can be attributed to four factors: the abundance of data accessible as training sets, the innovation in DNN model architecture, the commoditization of general-purpose massively parallel computing devices such as GPUs and TPUs to accelerate training, and the development of deep learning frameworks such as TensorFlow/PyTorch/MXNet to simplify the programming of sophisticated models. The thesis focuses on the aspect of deep learning frameworks.

Current DL systems [7, 8, 9, 10, 11] typically structure the design into two parts. A *frontend* lets users write programs using tensor operators. The dependencies among the operators are then recorded, declaratively or imperatively, in a *tensor dataflow graph* (or *tensor computation graph*), which is evaluated concretely in a *backend*. The frontend determines the programmability of the DL framework. By supporting many tensor operations or new programming primitives, the frontend could cover a wide range of DNNs. The backend determines the performance of DL framework. Most existing backends run on a single GPU, while more performance can be achieved if the backend can utilize multiple GPUs. However, deep learning research keeps pushing the limits of DL systems as newly

Figure 1.1: The growth of DNN model size.

developed DNN models become more complex in terms of both capacity and architecture. One major trend of DNN development is to increase the model size. As shown in figure 1.1, the AlexNet [1] model that achieved 16% prediction error in the ImageNet image classification challenge in 2012 has only 8 layers, while in 2015, the ResNet [2] model has 152 layers and achieved 3.5% prediction error. The BERT [4] model proposed in 2018 that topped several natural language processing tasks has 340 million parameters, and was surpassed a year later by the GPT-2 [12] model that has 1.5 billion parameters. Empirical evidence shows that, since the 80s, the number of parameters in the state-ofthe-art neural network has doubled roughly every 2.4 years [13]. As DNNs keep achieving impressive results with more data and parameters, training very large models beyond the capacity of a simple computing device (e.g., one GPU) becomes an immediate challenge to resolve.

Besides the scaling challenge, current DL systems are inadequate when dealing with the DNNs for structural data. These DNNs tend to define a computation over a sparse graph while current DL systems are highly optimized for dense tensor computation. As a result, users have to ponder implementation difficulty into model design. For example, the author of Graph Attention Networks [14] posted the following reply on OpenReview when was asked about the lack of result on Pubmed [15] dataset: "Unfortunately, even though

Figure 1.2: (a) Current DL system design. (b) SMEX system design.

the softmax computation on every node should be trivially parallelisable, we were unable to make advantage of our tensor manipulation framework to achieve this parallelisation, while retaining a favourable storage complexity ... and caused OOM errors on our GPU when the Pubmed dataset was provided.<sup>11</sup>. In fact, the Pubmed graph only has 20K nodes and 45K edges, which is several orders of magnitudes behind the scale of real-world graphs. Hence, an efficient and flexible system is highly desirable for training the DNNs for graph data.

The dissertation introduces two systems, Tofu and DGL, to address the two problems respectively. At a higher level, they share the same design principle we summarized as **SMEX**. Compared with the design of current DL systems, SMEX separates the semantic and runtime contexts to two stages and bridges them with a graph rewriter (figure 1.2). More precisely, the major components in the design are

- a semantic dataflow graph that includes the semantic specification of the involved tensor operations,

- a **dataflow graph rewriter** that analyzes the semantic dataflow graph and generates a new graph for execution,

<sup>1.</sup> https://openreview.net/forum?id=rJXMpikCZ

• and an **execution dataflow graph** that can efficiently run on one or multiple devices.

**Thesis Statement.** The SMEX design can effectively expand the capacity and the range of DNN models that a deep learning system can support.

We evaluate the statement by applying it to two systems (Tofu and DGL). Tofu targets the problem of training very large DNNs by partitioning and distributing the training to multiple computing devices. We design a domain-specific language which describes the fine-grained operator semantics. This allows the system to understand how to partition and parallelize each operator. We further develop an algorithm that can efficiently find the parallel strategy of an entire dataflow graph that is both load-balanced and communicationsaving. The result is that Tofu can scale to DNNs that are much larger and achieve better speedup compared to previous work.

The second system DGL focuses on the emerging field of geometric deep learning. Since the models are meant for sparse and irregular graph data, it is challenging to train them efficiently in the DL systems optimized for dense tensor computation. DGL proposes a general programming interface specifying how the models compute on one node or one edge, and then generates efficient tensor dataflow graph for execution. The evaluation shows that DGL outperforms other specialized GNN frameworks by a large margin and can scale to graph of millions of nodes.

In the remainder of the chapter, we discuss more motivations behind the SMEX design and then highlight some key contributions.

### 1.1 Challenges with existing DL systems

**Challenges in supporting very large DNNs** The size of a DNN model that can be explored today is constrained by the limited GPU device memory. There have been many efforts to tackle the problem. Some proposals try to fit larger models into a single GPU, e.g. by using the much larger CPU memory as a swap area for the GPU [16] or by discarding

intermediate results to save memory at the cost of re-computation [17, 18, 19]. Another promising solution is to partition a DNN model across multiple GPU devices. Doing so reduces per-GPU memory footprint and comes with the additional benefit of parallel speedup. This is commonly referred to as "model parallelism" in the literature.

A DNN model consists of a large number of layers, each parameterized by its own weights. There are two approaches to realize model parallelism. One approach is to assign the computation of different layers to different devices. The second approach is to partition the tensors to parallelize each layer across devices. For very large DNN models, tensor partitioning is the better approach; not only it results in balanced per-GPU memory usage but also it is necessary for speeding up popular models such as CNNs.

Early work on tensor partitioning [20, 21, 22] require users to manually partition tensors, which demands non-trivial analysis of the DNN architecture and implementation. Recent approaches [23, 24, 25] formulate it as an optimization problem and propose automatic solutions. However, they still rely on the knowledge on how to partition a few common layers, and thus support a limited type of DNN models. As a result, how to fully automate model partitioning for training very large DNNs remains a challenge.

**Challenges in supporting DNNs for graph data** A broad range of models can be unified as either learning from explicit or inferring latent structures. Examples include TreeL-STM [26] that works on sentence parsing trees, and the recent Graph Neural Networks (GNNs) family that aim to model a set of node entities together with their relationships (edges).

Unfortunately, existing tensor-based frameworks lack intuitive support for this trend of deep graph learning. Specifically, GNNs are defined using the message passing paradigm [6]. However, tensor-based frameworks do not support the message-passing interface. As such, researchers need to manually emulate graph computation using tensor operations, which poses an implementation challenge. Existing specialized tools [27] cannot fully utilize the sparse tensor operations involved in GNN training and hence cannot scale to graphs of moderate sizes. Moreover, none of the existing tools have support for GNNs over heterogeneous graphs.

### **1.2** Contributions

At a higher level, both challenges expose the same set of issues in current DL system design:

- Entangled semantic and system contexts: The dataflow graph in current DL systems expresses not only the actual training logic but also many system decisions such as device placement and communication pattern. Such practice is burdensome to the end user and also brittle to any changes of hardware environment and model architecture.

- Lacking operator semantics: The operators in existing DL systems are opaque and lack concrete semantics. In the case of automatic tensor partitioning, this prevents any solution to be applicable to a state-of-the-art DL system that can have hundreds of tensor operators. In terms of supporting DNNs for graphs, exposing operator semantics is vital to system optimizations such as automatic batching and fusion.

The SMEX system design tackles the problems in three steps. Firstly, a user program is directly represented by a *semantic dataflow graph* with few or no runtime contexts. Each operator has a specification describing how to compute each output element. The specification can be provided by an operator developer or naturally derived from a programming abstraction so that the effort is affordable. Secondly, a *dataflow graph rewriter* is in charge of transforming the semantic dataflow graph into an *execution dataflow graph*. The rewriter can implement algorithms to partition, fuse or batch operators for more parallelism as long as the two graphs produce the same result. The rewriter is also responsible of generating necessary device contexts and extra communication operators. Finally, the execution dataflow graph is evaluated by the existing DL system backend. The whole design is agnostic to the choice of DL platforms, making it widely applicable.

We then present two systems, Tofu and DGL, their technical contributions, and their connections to the SMEX design.

Tofu targets the scaling problem of training very large DNN models ( $\S$ 3). Given a DNN training program, Tofu aims to automatically partition every involved tensor and operator so that the partitioning is both memory-balanced and capable of accelerating the training. There are two technical challenges to resolve. (i) How to partition the input/output tensors and parallelize the execution an individual operator? What are the viable partition dimensions? (ii) how to optimize the partitioning of different operators for the overall graph? For (i), Tofu lets operator developers annotate operators in a lightweight Tensor Description Language (TDL). TDL describes tensor computation by specifying the output tensor value at each index with simple expressions over the input tensor elements. We then develop a technique based on symbolic execution to determine what input regions must be transferred across devices when a tensor are divided along a specific partition dimension  $(\S3.4.2)$ . For (ii), we formulate it as a combinatorial optimization problem that is proved to be NP-hard. We then propose several techniques to prune the search space including a recursive algorithm that can effectively reduce the search time from hours to seconds (§3.5.2). The results show that Tofu can train models that are  $6 \times$  larger on 8 GPUs and achieve 60% - 95% of the ideal efficiency.

#### SMEX design in Tofu

- Semantic dataflow graph: A dataflow graph with TDL descriptions.

- **Dataflow graph rewriter:** Responsible for analyzing TDL annotations, discovering viable partition dimensions for individual operators, searching for global parallel strategy and generating the partitioned dataflow graph.

- Execution dataflow graph: A partitioned dataflow graph that can be executed on multiple devices.

DGL is a new framework for DNNs for structural data such as TreeLSTM and the models of the GNN family (§4). Following the message passing paradigm [6], DGL provides intuitive message passing programming interface, which describes the computation on a batch of nodes and edges (§4.5). Converting the program to an efficient tensor dataflow graph for execution requires batching. However, previous auto-batching approaches [28, 29] incur significant overhead from dataflow graph construction. By contrast, DGL forms batches by analyzing the input graph and generates the dataflow graph for a batch of nodes, giving an up to  $10 \times$  speedup (§4.6.1). Furthermore, we develop a kernel fusion technique that avoids storing explicit messages, significantly improve both memory consumption and training speed (§4.6.2). As a result, DGL can scale to graphs with hundreds of millions of edges, and can train up to  $7.5 \times$  faster than other specialized GNN frameworks.

SMEX design in DGL

- Semantic dataflow graph: A dataflow graph with operators described in message passing paradigm.

- Dataflow graph rewriter: Responsible for analyzing graph structure, autobatching and kernel fusion.

- Execution dataflow graph: A dataflow graph with batched or fused operators.

### 1.3 Roadmap

The rest of the dissertation is organized as follows. Chapter 2 discusses more details about related backgrounds including the evolution of deep learning systems and the prior work for machine learning on graphs. Chapter 3 describes the overall design of Tofu, its technical solutions and evaluations. We also provide a theoretical analysis of the proposed recursive search algorithm in Appendix A. Chapter 4 discusses in detail the challenges of building a graph DNN system, and explains how the programming interface and optimization techniques of DGL address them. Finally, Chapter 5 summarizes this work, lists its limitations and provides an outlook of future directions.

# Chapter 2

# **Related Work**

### 2.1 Deep Learning Systems

The growing interest in deep learning leads to an explosion of specialized tools and systems over the decade. Early tools such as Cuda-Convnet [30], Caffe [31] and CXXNet [32] let users write a configuration script consisting of a stack of common neural network layers and their hyper-parameters. The models are trained by some built-in, opaque routines that perform forward and backward propagation. The design heavily targets the DNNs used in computer vision, by resembling the construction of feed-forward neural networks, at a cost of support of models like recurrent neural networks. Seeing the incompetence, frameworks such as Torch [33] and Theano [34] provide an *tensor programming interface*, which expresses neural networks by operators of multi-dimensional arrays (or tensors) and embeds them into popular programming languages such as Lua, Python and C++. Although these frameworks are capable of accelerating DNN training by utilizing specialized operator libraries such as cuDNN [35] and MKLDNN [36], training models in scale remains a challenge.

Inspired by the dataflow systems for cluster computing [37, 38, 39], modern deep learning systems such as MXNet [7], Tensorflow [8], Caffe2 [9], Chainer [10], PyTorch [11] and

Figure 2.1: (a) A Multi-Layer Perceptron (MLP) model; (b) The dataflow graph for its forward and backward propagations.

Minerva [21] tackle the scalability challenge by translating the DNN training program in array-based interface into tensor dataflow graph representation. At its core, a tensor dataflow graph is a directed acyclic graph consisting of two types of nodes: tensor and operator. An edge connects either a tensor node to its producer or consumer operators or two operator nodes indicating the data dependency. Figure 2.1 shows an example dataflow graph for the forward and backward propagation of a Multi-Layer Perceptron (MLP) model. The weights of neuron connections between successive layers l and l + 1are represented by matrix  $W_l$ . The forward propagation calculates the training loss Cby repeatedly computing the activation of a layer from its preceding layer. Specifically,  $x_{l+1} = f(x_l \cdot W_l)$ , where layer l's activation vector  $x_l$  is multiplied with the weight matrix  $W_l$  and then scaled using an element-wise non-linear function f. After that, the backward propagation calculates the gradient matrix  $\frac{dC}{dW_l}$  of each weight matrix  $W_l$  from higher to lower layers. The dataflow graph thus consists of two towers for the two passes.

Using tensor dataflow graph to represent DNN training has many benefits. Firstly, the backward computation following the chain rule can be derived automatically from the dataflow graph for the forward computation. In the simple example, we could roughly observe the correspondence between the two towers; for each matrix multiplication MatMul or non-linear function f in the forward pass, there is the derivative function dMatMul or df in the backward pass. Auto-differentiation has been the de-facto equipment in modern DL systems, an essential enabler for training deep and complex neural networks.

Secondly, dataflow graph representation allows modern DL systems to train DNNs more efficiently because operators with no data dependency can be executed in parallel, which suits well with multi-threading execution on CPU and multi-stream model on GPU. Another benefit from an articulate expression of parallelism is that it eases the system design for distributed training by naturally overlapping independent network communication with computation. Built upon it, many research work have explored different approaches for parallelizing DNN training, which we elaborate in §2.2.

Another question is how to extract dataflow graph representation from user programs, and perhaps more importantly, how to design the programming interface? There are two considerations. On one hand, there has been a long history of programming machine learning algorithms in a dynamic scripting language such as Python, which proven to be very productive. On the other hand, efficient execution and many program analysis and optimization techniques require a strongly-typed static language. To strike a balance, DL systems such as Tensorflow and MXNet adopt a declarative programming interface. Users express training logic such as loss and gradient calculation symbolically in a domainspecific language (DSL) embedded in a dynamic language (e.g. Python), and perform concrete evaluation afterwards. This design leans towards execution efficiency at a cost of debuggability and usability because it artificially segments a user program into declaration and execution parts. With the explosion of DL research, DL systems shift more and more toward the productivity end. PyTorch, MXNet Gluon [40] and Tensorflow v2.0 all focus on imperative programming paradigm, where each tensor operator not only records data dependency but also concretely calculates the result. The insight is that although such dynamic execution mode (or eager mode) misses certain optimization chances when the

Figure 2.2: Data parallelism and model parallelism

whole program is available, the strong coherence between two training iterations fuels many runtime optimization techniques such as cached memory allocator, leading to competitive performance compared to symbolic mode [11].

A dataflow graph, no matter how it is extracted, is a form of intermediate representation (IR) of a user program, which by design is conductive for further optimization and translation. Many previous work have proposed techniques based on dataflow graph for memory optimization [19, 17], auto-batching [29, 28] and smart device placement [41]. NNVM [42] and ONNX [43] further define a unified and canonical dataflow format to enable the interoperability between different frameworks and streamline the path from research to production. However, dataflow representation has the fundamental defect for expressing control flows which limits its applicable scope. The rise of *differentiable programming paradigm*<sup>1</sup> pushes new IRs being developed [44, 45] that are both universal (i.e. Turing complete) and strongly-typed array language, which opens up new research directions such as auto-differentiation techniques [46, 47] and optimizations.

### 2.2 Parallel DNN Training

The most widely used method for scaling DNN training today is **data parallelism**. Traditional DNN training is based on batched stochastic gradient descent where the batch

<sup>1.</sup> https://www.facebook.com/yann.lecun/posts/10155003011462143

size is kept deliberately small. Within a batch, computation on each sample can be carried out independently and aggregated at the end of the batch. Data parallelism divides a batch among several GPU devices and incurs cross-device communication to aggregate and synchronize model parameters at the end of each batch using a parameter service [48, 49].

Data parallelism has achieved good speedup for some DNN models (e.g. Inception network [50]). However, since the communication overhead of data parallelism increases as the model grows bigger, one must train using a very large batch size to amortize the communication cost across many devices. In fact, for any DNN model, one can always scale the "training throughput" by ever increasing the batch size. Unfortunately, large batch training is known to be problematic such as longer convergence time or decreased model accuracy [51, 22].

Model parallelism partitions the model parameters of each layer among devices, so that the update of parameters can be performed locally (Figure 2.2). Each device can only calculate part of a layer's activation using its parameter partition, so all devices need to synchronize their activations and activation gradients for each layer during both the forward and backward propagations. Since model parallelism exchanges activations instead of the model parameters, it works well for models with small activation size such as DNN models with large fully-connected layers.

The trade-off between data and model parallelism leads to the development of more complex strategies. For examples, **mixed parallelism** [22] distributes some DNN layers using data parallelism while using model parallelism for others. **Combined parallelism** divides workers into groups and uses different strategies for inter-group and intra-group communication. Combined parallelism was proposed in the earlier generation of specialized training systems [48, 52], but is not thoroughly explored due to its programming complexity.

# Chapter 3

# Tofu: Supporting Very Large Models using Automatic Dataflow Graph Partitioning

In this chapter, we applied the SMEX design to the context of partitioning dataflow graph for training very large models. We will show that by separating the design into semantic and execution dataflow graphs, Tofu can efficiently utilize the aggregated memory capacity of multiple devices for training very large models with very little user effort.

#### **3.1** Introduction

The deep learning community has been using larger deep neural network (DNN) models to achieve higher accuracy on more complex tasks over the past few years [53, 54]. Empirical evidence shows that, since the 80s, the number of parameters in the state-of-the-art neural network has doubled roughly every 2.4 years [13], enabled by hardware improvements and the availability of large datasets. As deployed DNN models remain many orders of magnitude smaller than that of a mammalian brain, there remains much room for growth. However, the size of a DNN model that can be explored today is constrained by the limited GPU device memory. There have been many efforts to tackle the problem of limited GPU device memory. Some proposals try to fit larger models into a single GPU, e.g. by using the much larger CPU memory as a swap area for the GPU [16] or by discarding intermediate results to save memory at the cost of re-computation [17, 18, 19]. Another promising solution is to partition a DNN model across multiple GPU devices. Doing so reduces per-GPU memory footprint and comes with the additional benefit of parallel speedup. This is commonly referred to as "model parallelism" in the literature.

A DNN model consists of a large number of layers, each parameterized by its own weights. There are two approaches to realize model parallelism. One approach is to assign the computation of different layers to different devices. The second approach is to partition the tensors to parallelize each layer across devices. For very large DNN models, tensor partitioning is the better approach; not only it results in balanced per-GPU memory usage but also it necessary for speeding up popular models such as CNNs.

Tensor partitioning has been explored by existing work as a means for achieving parallel speedup [48, 20, 52] or saving memory access energy [55, 56]. Recent proposals [23, 24, 25] support partitioning a tensor along multiple dimensions and can automatically search for the best partition dimensions. The major limitation is that these proposals partition at the coarse granularity of individual DNN layers, such as fully-connected and 2D convolution layers. As such, they either develop specialized implementation for specific models [23, 20] or allow only a composition of common DNN layers [24, 25, 48, 52].

However, the vast majority of DNN development and deployment today occur on general-purpose deep learning platforms such as TensorFlow [8], MXNet [7], PyTorch [11]. These platforms represent computation as a dataflow graph of fine-grained tensor operators, such as matrix multiplication, various types of convolution and element-wise operations etc. Can we support tensor partitioning on one of these general-purpose platforms? To do so, we have built the Tofu system to automatically partition the input/output tensors of each operator in the MXNet dataflow system. This approach, which we call *operator*  *partitioning*, is more fine-grained than layer partitioning. While we have built Tofu's prototype to work with MXNet, Tofu's solution is general and could potentially be applied to other dataflow systems such as TensorFlow.

In order to partition a dataflow graph of operators, Tofu must address two challenges. 1) How to partition the input/output tensors and parallelize the execution an individual operator? What are the viable partition dimensions? 2) how to optimize the partitioning of different operators for the overall graph? Both challenges are made difficult by the fine-grained approach of partitioning operators instead of layers. For the first challenge, existing work [23, 24, 25] manually discover how to partition a few common layers. However, a dataflow framework supports a large and growing collection of operators (e.g. 139 in MXNet), intensifying the manual efforts. Manual discovery is also error-prone, and can miss certain partition strategies. For example, [24] misses a crucial partition strategy that can significantly reduce per-worker memory footprint (§3.7.3). For the second challenge, existing proposals use greedy or dynamic-programming based algorithms [23, 24] or stochastic searches [25]. As the graph of operators is more complex and an order of magnitude larger than the graph of layers (e.g. the graph for training a 152-layer ResNet has >1500 operators in MXNet), these algorithms become inapplicable or run too slowly (§3.5, Table 3.1).

Tofu introduces novel solutions to address the above mentioned challenges. To enable the automatic discovery of an operator's partition dimensions, Tofu requires developers to specify what the operator computes using a lightweight description language called TDL. Inspired by Halide [57], TDL describes tensor computation by specifying the output tensor value at each index with simple expressions on the input tensors. The Halide-style description is useful because it makes explicit which input tensor regions are needed in order to compute a specific output tensor region. Thus, Tofu can statically analyze an operator's TDL description using symbolic execution to determine what input regions must be transferred among GPUs when tensors are divided along a specific partition dimension. To partition each tensor in the overall dataflow graph, we propose several techniques to shrink the search space. These include a recursive search algorithm which partitions the graph among only two workers at each recursive step, and graph coarsening by grouping related operators.

We have implemented a prototype of Tofu in MXNet and evaluated its performance on a single machine with eight GPUs. Our experiments use large DNN models including Wide ResNet [53] and Multi-layer Recurrent Neural Networks [58], most of which do not fit in a single GPU's memory. Compared with other approaches to train large models, Tofu's training throughput is 25% - 400% higher.

To the best of our knowledge, Tofu is the first system to automatically partition a dataflow graph of fine-grained tensor operators. Though promising, Tofu has several limitations. Some operators (e.g. Cholesky) cannot be expressed in TDL and thus cannot be automatically partitioned. The automatically discovered partition strategies do not exploit the underlying communication topology. Tofu is also designed for very large DNN models. For moderately sized models that do fit in the memory of a single GPU, Tofu's approach of operator partitioning are likely no better than the much simpler approach of data parallelism. Removing these limitations requires further research.

#### **3.2** Problem settings

**The problem.** Training very large DNN models is limited by the size of GPU device memory today. Compared with CPU memory, GPU memory has much higher bandwidth but also smaller capacity, ranging from 12GB (NVIDIA K80) to 16GB (NVIDIA Tesla V100). Google's TPU hardware has similar limitations, with 8GB attached to each TPU core [59].

Partitioning each tensor in the DNN computation across multiple devices can lower per-GPU memory footprint, thereby allowing very large models to be trained. When par-

Figure 3.1: The naive implementation of conv1d in Python.

titioning across k devices, each device roughly consumes  $\frac{1}{k}$  times the total memory required to run the computation on one device. Furthermore, partitioning also has the important benefit of performance speedup via parallel execution. As most DNN development today is done on dataflow platforms such as TensorFlow and MXNet, our goal is to automatically partition the tensors and parallelize the operators in a dataflow graph to enable the training of very large DNN models. The partitioning should be completely transparent to the user: the same program written for a single device can also be run across devices without changes.

**System setting.** When tensors are partitioned, workers must communicate with each other to fetch the data needed for computation. The amount of bytes transferred divided by the computation time forms a lower bound of the communication bandwidth required to achieve competitive performance. For training very large DNNs on fast GPUs, the aggregate bandwidth required far exceeds the network bandwidth in deployed GPU clusters (e.g. Amazon's EC2 GPU instances have only 25Gbps aggregate bandwidth). Thus, for our implementation and evaluation, we target a single machine with multiple GPU devices.

### **3.3** Challenges and our approach

In order to partition a dataflow graph of operators, we must tackle the two challenges mentioned in §3.1. We discuss these two challenges in details and explain at a high level how Tofu solves them.

#### 3.3.1 How to partition a single operator?

To make the problem of automatic partitioning tractable, we consider only a restricted parallelization pattern, which we call "**partition-n-reduce**". Suppose operator c computes output tensor O. Under partition-n-reduce, c can be parallelized across two workers by executing the *same* operator on each worker using smaller inputs. The final output tensor O can be obtained from the output tensors of both workers ( $O_1$ , and  $O_2$ ) in one of the two ways. 1) O is the concatenation of  $O_1$  and  $O_2$  along some dimension. 2) O is the elementwise reduction of  $O_1$  and  $O_2$ . Partition-n-reduce is crucial for automatic parallelization because it allows an operator's existing single-GPU implementation to be re-used for parallel execution. Such implementation often belongs to a highly optimized closed-source library (e.g. cuBLAS, cuDNN).

Partition-n-reduce is not universally applicable, e.g. Cholesky [60] cannot be parallelized this way. Nor is partition-n-reduce optimal. One can achieve more efficient communication with specialized parallel algorithms (e.g. Cannon's algorithm [61] for matrix multiplication) than with partition-n-reduce. Nevertheless, the vast majority of operators can be parallelized using partition-n-reduce (§3.4.1) and have good performance.

Tensors used in DNNs have many dimensions so there are potentially many different ways to parallelize an operator. Figure 3.1 shows an example operator, conv1d, which computes 1-D convolution over data using filters. The 3-D data tensor contains a batch (b) of 1-D pixels with ci input channels. The 3-D filters tensor contains a convolution window for each pair of ci input and co output channel. The 3-D output tensor contains

Figure 3.2: Two of several ways to parallelize conv1d according to partition-n-reduce. Each 3D tensor is represented as a 2D matrix of vectors. Different stripe patterns show the input tensor regions required by different workers.

the convolved pixels for the batch of data on all output channels.

There are many ways to parallelize conv1d using partition-n-reduce; Figure 3.2 shows two of them. In Figure 3.2(a), the final output is a concatenation (along the b dimension) of output tensors computed by each worker. Each worker reads the entire filters tensor and half of the data tensor. In Figure 3.2(b), the final output is a reduction (sum) of each worker's output. Figure 3.1 shows what input tensor region each work reads from. If tensors are partitioned, workers must perform remote data fetch.

Prior work [23, 24, 25] manually discovers the partition strategies for a few common DNN layers. Some [24, 25] have ignored the strategy that uses output reduction (i.e. Figure 3.2(b)), which we show to have performance benefits later (§3.7.3). Manual discovery is tedious for a dataflow system with a large number of operators (341 and 139 in TensorFlow and MXNet respectively). Can one support automatic discovery instead?

**Our approach.** Tofu analyzes the access pattern of an operator to determine all viable partition strategies. As such, we require the developer of operators to provide a succinct description of what each operator computes in a light-weight language called TDL (short for Tensor Description Language). An operator's TDL description is separate from its implementation. The description specifies at a high-level how the output tensor is derived from its inputs, without any concern for algorithmic or architectural optimization, which are handled by the operator's implementation. We can statically analyze an operator's TDL description to determine how to partition it along different dimensions. §3.4 describes this part of Tofu's design in details.

#### 3.3.2 How to optimize partitioning for a graph?

As each operator has several partition strategies, there are combinatorially many choices to partition each tensor in the dataflow graph, each of which has different execution time and per-GPU memory consumption.

It is a NP-hard problem to partition a general dataflow graph for optimal performance [62, 63, 64, 65]. Existing proposals use greedy or dynamic-programming algorithm to optimize a mostly linear graph of layers [23, 24], or perform stochastic searches [25, 41, 66] for general graphs. The former approach is faster, but still impractical when applied on fine-grained dataflow graphs. In particular, its running time is proportional to the number of ways an operator can be partitioned. When there are  $2^m$  GPUs, each input/output tensor of an operator can be partitioned along a combination of any 1, 2, ..., or *m* dimensions, thereby dramatically increasing the number of partition strategies and exploding the search time.

**Our approach.** We use an existing dynamic programming (DP) algorithm [24] in our search and propose several key techniques to make it practical. First, we leverage the unique characteristics of DNN computation to "coarsen" the dataflow graph and shrink the search space. These include grouping the forward and backward operations, and coalescing element-wise or unrolled operators. Second, to avoid blowing up the search space in the face of many GPUs, we apply the basic search algorithm recursively. In each recursive step, the DP algorithm only needs to partition each tensor in the coarsened graph among

```

@tofu.op

def conv1d(data, filters):

return lambda b, co, x:

Sum(lambda ci, dx: data[b, ci, x+dx]*filters[ci, co, dx])

@tofu.op

def batch_cholesky(batch_mat):

Cholesky = tofu.Opaque()

return lambda b, i, j: Cholesky(batch_mat[b, :, :])[i,j]

```

Figure 3.3: Example TDL descriptions.

two "groups" (of GPUs). §3.5 describes this part of Tofu's design in details.

### 3.4 Partitioning a single operator

This section describes TDL (\$3.4.1) and its analysis (\$3.4.2).

#### 3.4.1 Describing an operator

Our Tensor Description Language (TDL) is inspired by Halide[57]. The core idea is "tensor-as-a-lambda", i.e. we represent tensors as lambda functions that map from coordinates (aka index variables) to values, expressed as a TDL expression. TDL expressions are side-effect free and include the following:

- Index variables (i.e. arguments of the lambda function).

- Tensor elements (e.g. filters[ci, co, dx]).

- Arithmetic operations involving constants, index variables, tensor elements or TDL expressions.

- Reduction over a tensor along one or more dimensions.

*Reducers* are commutative and associative functions that aggregate elements of a tensor along one or more dimensions. Tofu supports Sum, Max, Min and Prod as built-in reducers. It is possible to let programmers define custom reducers, but we have not encountered the need to do so.

We implemented TDL as a DSL using Python. As an example, Figure 3.3 shows the description of conv1d, whose output is a 3D tensor defined by lambda b, co, x: ... Each element of the output tensor is the result of reduction (Sum) over an internal 2D tensor (lambda ci, dx: ...) over both ci and dx dimensions.

**Opaque function.** We have deliberately designed TDL to be simple and not Turingcomplete. For example, TDL does not support loops or recursion, and thus cannot express sophisticated computation such as Cholesky decomposition. In such cases, we represent the computation as an *opaque function*. Sometimes, such an operator has a batched-version that can be partitioned along the batch dimension. Figure 3.3 shows the TDL description of the operator batch\_cholesky. The output is a 3-D tensor (lambda b,i,j:...) where the element at (b, i, j) is defined to be the (i, j) element of the matrix obtained from performing Cholesky on the *b*-th slice of the input tensor. Note that, batch\_mat[b, :, :] represents the b<sup>th</sup> slice of the batch\_mat tensor. It is syntactic sugar for the lambda expression lambda r, c: batch\_mat[b, r, c].

**Describing MXNet operators in TDL.** Ideally, operator developers should write TDL descriptions. As Tofu is meant to work with an existing dataflow system (MXNet), we have written the descriptions ourselves as a way to bootstrap. We found that TDL can describe 134 out of 139 MXNet v0.11 operators. Out of these, 77 are simple element-wise operators; 2 use the opaque function primitive, and 11 have output reductions. It takes one of the authors one day to write all these descriptions; most of them have fewer than three LoC. Although we did not build Tofu's prototype for TensorFlow, we did investigate how well TDL can express TensorFlow operators. We found that TDL can describe 257 out of 341 TensorFlow operators. Out of these, 140 are element-wise operators; 22 use the opaque function. For those operators that cannot be described by TDL, they belong to

three categories: sparse tensor manipulations, operators with dynamic output shapes and operators requiring data-dependent indexing. MXNet has no operators in the latter two categories.

**TDL vs. other Halide-inspired language.** Concurrent with our work, TVM [67] and TC [68] are two other Halide-inspired DSLs. Compared to these DSLs, TDL is designed for a different purpose. Specifically, we use TDL to analyze an operator's partition strategies while TVM and TC are designed for code generation to different hardware platforms. The different usage scenarios lead to two design differences. First, TDL does not require users to write intricate execution schedules – code for describing how to perform loop transformation, caching, and mapping to hardwares, etc. Second, TDL supports opaque functions that let users elide certain details of the computation that are not crucial for analyzing how the operator can be partitioned.

### 3.4.2 Analyzing TDL Descriptions

Tofu analyzes the TDL description of an operator to discover its basic partition strategies. A basic partition strategy parallelizes an operator for 2 workers only. Our search algorithm uses basic strategies recursively to optimize partitioning for more than two workers ( $\S3.5.2$ ).

A partition strategy can be specified by describing the input tensor regions required by each worker to perform its "share" of the computation. This information is used later by our search algorithm to optimize partitioning for the dataflow graph and to generate the partitioned graph in which required data is fetched from different workers.

Obtaining input regions from a TDL description is straightforward if tensor shapes are known. For example, consider the following simple description:

def shift\_two(A): B = lambda i : A[i+2]; return B

Suppose we want to partition along output dimension i. Given i's concrete range, say [0,9], we can compute that the worker needs A's data over range [2,6] (or [7,11]) in order to compute B over range [0,4] (or [5,9]).

Analyzing with concrete ranges is hugely inefficient as a dataflow graph can contain thousands of operators, many of which are identical except for their tensor shapes (aka index ranges). Therefore, we perform TDL analysis in the abstract domain using *symbolic interval analysis*, a technique previously used for program variable analysis[69], boundary checking[70], parameter validation[71].

Symbolic interval analysis. Suppose the output tensor of an operator has n dimensions and is of the form lambda x1, ..., xn : .... We consider the range of index variable xi to be  $[0, \mathcal{X}_i]$ , where  $\mathcal{X}_i$  is a symbolic upper bound. We then symbolically execute the lambda function to calculate the symbolic intervals indicating the range of access on the operator's input tensors.

Symbolic execution should keep the range as precise as possible. To do so, we represent symbolic interval  $(\mathcal{I})$  as an affine transformation of all symbolic upper bounds,

$$\mathcal{I} \triangleq [\Sigma_i l_i \mathcal{X}_i + c, \ \Sigma_i u_i \mathcal{X}_i + c], l_i, u_i, c \in \mathbb{R}$$

(3.1)

In equation 3.1,  $l_i$ ,  $u_i$  and c are some constants. Thus, we can represent  $\mathcal{I}$  as a vector of 2 \* n + 1 real values  $\langle l_1, ..., l_n, u_1, ..., u_n, c \rangle$ . Let  $\mathsf{ZV}[u_i = a]$  denote a vector of all 0s except for the position corresponding to  $u_i$  which has value a. By default, lambda variable xi for dimension i is initialized to  $\mathsf{ZV}[u_i = 1]$ .

Our representation can support affine transformation on the intervals, as shown by the allowed interval arithmetic in Figure 3.4. Product or comparison between two intervals are not supported and will raise an error. We did not encounter any such non-affine operations among MXNet operators.

TDL description: lambda x1, ..., xi, ..., xn: ...,

$$\mathcal{I} \triangleq \langle l_1, ..., l_n, u_1, ..., u_n, c \rangle$$

$\mathcal{I} \pm k, k \in \mathbb{R} = \langle l_1, ..., l_n, u_1, ..., u_n, c \pm k \rangle$

$\mathcal{I} \times k, k \in \mathbb{R} = \langle l_1k, ..., l_nk, u_1k, ..., u_nk, c * k \rangle$

$\mathcal{I}/k, k \in \mathbb{R} = \langle l_1/k, ..., l_n/k, u_1/k, ..., u_n/k, c/k \rangle$

$\mathcal{I} \pm \mathcal{I}' = \langle l_1 \pm l'_1, ..., u_1 \pm u'_1, ..., c \pm c' \rangle$

Figure 3.4: Tofu's symbolic interval arithmetic.

**Discover operator partition strategies.** Using the symbolic interval analysis, we infer the input regions required by each of the 2 workers for every partitionable dimension. There are two cases.

*Case-1* corresponds to doing partition-n-reduce without the reduction step. In this case, each partition strategy corresponds to some output dimension. Suppose we are to partition conv1d's output tensor along dimension b. We use two different initial intervals for lambda variable b,  $ZV[u_b = \frac{1}{2}]$  and  $ZV[l_b = \frac{1}{2}, u_b = 1]$ , in two separate analysis runs. Each run calculates the input regions needed to compute half of the output tensor. The result shows that that each worker reads half of the data tensor partitioned on the b dimension and all of the filter tensor, as illustrated in Figure 3.2(a). Similarly, the analysis shows how to partition the other output dimensions, co and x. Partitioning along dimension x is commonly referred to as parallel convolution with "halo exchange" [20, 23, 56].

*Case-2* corresponds to doing partition-n-reduce with the reduction step. In this case, we partition along a reduction dimension. In the example of Figure 3.3, the reduction dimensions corresponding to ci and dx in Sum(lambda ci, dx: ...). The analysis will determine that, when partitioning along ci, each partially reduced tensor will require half of the data tensor partitioned on the second dimension and half of the filter tensor partitioned on the first dimension, as shown in Figure 3.2(b). Similar analysis is also done for dimension dx. Out of 47 non-element-wise MXNet operators describable by TDL, 11 have at least one reduction dimension.

### 3.5 Partitioning the dataflow graph

To partition a dataflow graph, one needs to specify which partition strategy to use for each operator. This section describes how Tofu finds the best partition plan for a dataflow graph.

Different plans result in different running time and per-worker memory consumption, due to factors including communication, GPU kernel efficiency and synchronization. Finding the best plan is NP-hard for an arbitrary dataflow graph [72]. Recent work has proposed an algorithm based on dynamic programming (DP) for partitioning a certain type of graphs. §3.5.1 presents techniques to make a dataflow graph applicable to DP, and §3.5.2 improves search time via recursion.

**Optimization goal.** Ideally, our optimization goal should consider both the end-to-end execution time of the partitioned dataflow graph and the per-worker memory consumption. Unfortunately, neither metric can be optimized perfectly. Prior work [25] optimizes the approximate end-to-end execution time by minimizing the sum of total GPU kernel execution time and total data transfer time.

In Tofu, we choose to minimize the total communication cost based on two observations. First, the GPU kernels for very large DNN models process large tensors and thus have similar execution time no matter which dimension its input/output tensors are partitioned on. Consequently, a partition plan with lower communication cost tends to result in lower end-to-end execution time. Second, the memory consumed at each GPU worker is used in two areas: (1) for storing a worker's share of tensor data, (2) for buffering data for communication between GPUs. The memory consumed for (1) is the same for every partition plan: for k GPUs, it is always 1/k times the memory required to run the dataflow graph on one GPU. The memory consumed for (2) is proportional to the amount of communication. Therefore, a partition plan with lower communication cost results in a

Figure 3.5: (a) Layer graph of a MLP model. (b) Its dataflow graph including forward and backward computation (in grey). (c) Coarsened graph. For cleanness, we only illustrate one operator group, one group for activation tensors and one group for weight tensor (dashed lines).

smaller per-worker memory footprint.

### 3.5.1 Graph coarsening

The algorithm in [24] is only applicable for linear graphs<sup>1</sup>, such as the graph of DNN layers shown in Figure 3.5(a). Dataflow graphs of fine-grained operators are usually non-linear. For example, Figure 3.5(b) is the non-linear dataflow graph of the same DNN represented by Figure 3.5(a). Here, we propose to "coarsen" a dataflow graph into a linear one by grouping or coalescing multiple operators or tensors.

Grouping forward and backward operations. Almost all DNN models are trained using gradient-based optimization method. The training includes a user-written forward propagation phase to compute the loss function and a system-generated backward propagation phase to compute the gradients using the chain rule. Thus, we coarsen as follows:

• Each forward operator (introduced by the user) and its auto-generated backward operators (could be more than one) to form a group.

<sup>1.</sup> We say a graph G is linear if it is homeomorphic to a chain graph G', meaning there exists a graph isomorphism from some subdivision of G to some subdivision of G' [73]. Note that a "fork-join" style graph is linear by this definition.

• Each forward tensor (e.g. weight or intermediate tensors) and its gradient tensor form a group. If a (weight) tensor is used by multiple operators during forward propagation and thus has multiple gradients computed during backward propagation, the chain rule requires them to be summed up and the summation operator is added to the group as well.

Figure 3.5(c) shows the coarsened dataflow graph for a MLP model. As forward and backward operators for the same layer are grouped together, the resulting graph becomes isomorphic to the forward dataflow graph. For MLPs and CNNs, their coarsened graphs become linear. We perform the DP-based algorithm [24] on the coarsened graph. When the algorithm adds a group in its next DP step, we perform a brute-force combinatorial search among all member operators/tensors within the group to find the minimal cost for adding the group. This allows tensors involved in the forward and backward operators to be partitioned differently, while [24] forces them to share the same partition configurations. As there are only a few operators (typically 2) in each group, the cost of combinatorial search is very low.

**Coalescing operators.** In DNN training, it makes sense for some operators to share the same partition strategy. These operators can be merged into one in the coarsened dataflow graph. There are two cases:

- Merging consecutive element-wise operators, because the input and output tensors of an element-wise operator should always be partitioned identically. We analyze the TDL description to determine if an operator is element-wise. Consecutive elementwise operators are very common in DNN training. For instance, almost all gradientbased optimizers (e.g. SGD, Adam, etc.) are composed of only element-wise operators.

- *Merging unrolled timesteps*. Recurrent neural networks (RNNs) process a variable sequence of token over multiple timesteps. RNN has the key property that different

Figure 3.6: Recursively partition a dataflow graph to four workers. Only one matrix multiplication is drawn for cleanness. In step#1, every matrix is partitioned by row, and for group#0, B[1,:] is fetched from the other group. Because of this, B[1,:] becomes an extra input in step#2 when the graph is further partitioned to two workers. Because step#2 decides to partition every matrix by column, every matrix is partitioned into a 2x2 grid, with each worker computes one block.

|                    | Search Time |              |  |

|--------------------|-------------|--------------|--|

|                    | WResNet-152 | RNN-10       |  |

| Original DP [24]   | n/a         | n/a          |  |

| DP with coarsening | 8 hours     | >24 hours    |  |

| Using recursion    | 8.3 seconds | 66.6 seconds |  |

Table 3.1: Time to search for the best partition for 8 workers. WRestNet-152 and RNN-10 are two large DNN models described in §3.7.

time steps share the same computation logic and weight tensors. Thus, they should be coalesced to share the same partition strategy. As a result, the dataflow graph of a multi-layer RNN becomes a chain of coalesced and grouped operators. To detect operators that belong to different timesteps of the same computation, we utilize how RNN is programmed in DNN frameworks. For example, systems like MXNet and PyTorch call a built-in function to unroll a basic unit of RNN computation into many timesteps, allowing Tofu to detect and merge timesteps.

### 3.5.2 Recursive partitioning

When there are more than two workers, each operator can be partitioned along multiple dimensions. This drastically increases the number of partition strategies available to each operator and explodes the running time of the DP-based search algorithm. To see this, consider the coarsened graph of Figure 3.5(b). Every operator group has two input tensor groups and one output tensor group. Each tensor group contains one forward tensor and one gradient tensor. At each step, the DP algorithm needs to consider all the possible configurations of an operator group including different ways to partition the six input/output tensors. For each 4D tensor used in 2D-convolution, there are in total 20 different ways to partition it evenly across 8 workers. Hence, the number of possible configurations of 2D-convolution's operator group is  $20^6 = 6.4 \times 10^7$ . Although not all the dimensions are available for partition in practice (e.g. the convolution kernel dimension is usually very small), the massive search space still results in 8 hours of search time when partitioning the WResNet-152 model (Table 3.1).

Our insight is that the basic DP search algorithm can be *recursively* applied. For instance, a matrix, after being first partitioned by row, can be partitioned again. If the second partition is by column, the matrix is partitioned into a  $2\times 2$  grid; if the second partition is by row, the matrix is partitioned into four parts along the row dimension.

This observation inspires our recursive optimization algorithm to handle  $k = 2^m$  GPUs:

- Given a dataflow graph G, run the DP algorithm with coarsening to partition G for two worker groups, each consisting of 2<sup>m-1</sup> workers. Note that each tensor is only partitioned along one dimension.

- Consider the partitioned dataflow graph as consisting of two halves: G<sub>0</sub> for worker group#0 and G<sub>1</sub> for worker group#1. Each half also contains the data fetched from the other group as extra input tensors.

- 3. Repeat step 1 on  $G_0$  and apply the partition result to  $G_1$  until there is only one worker per group.

This recursive algorithm naturally supports partitioning along multiple dimensions. Figure 3.6 illustrates two recursive steps using an example dataflow graph (for brevity, we only show one matrix multiplication operator in the graph). Note the recursion must be done over the entire dataflow graph instead of a single operator, as the partition plan of the previous recursive step will influence the global decision of the current one.

While the recursive algorithm may seems straightforward, it is less obvious why the resulting partition plan has the optimal overall communication cost. In particular, the recursive algorithm chooses a sequence of basic partition plans  $\{\mathcal{P}_1, \mathcal{P}_2, ... \mathcal{P}_m\}$  in *m* recursive steps, and we need to prove that no other sequence of choices leads to a better plan with a smaller communication cost. The main insight of our proof is that the partition plan decided in each recursive step is commutative (i.e., choosing partition plan  $\mathcal{P}$  followed by  $\mathcal{P}'$  results in the same total communication cost as choosing  $\mathcal{P}'$  followed by  $\mathcal{P}$ .) Based on this insight, we derive the following property and use it to prove optimality.

**Theorem ??.** Let the total communication cost incurred by all worker groups at step *i* be  $\delta_i$ . Then  $\delta_i \leq \delta_{i+1}$ .

Suppose  $\{\mathcal{P}_1, \mathcal{P}_2, ... \mathcal{P}_m\}$  is the sequence of partition plans chosen and it is not optimal. Then there exists a different sequence  $\{\mathcal{P}'_1, \mathcal{P}'_2, ... \mathcal{P}'_m\}$  with smaller total cost. Hence, there must be two consecutive steps k - 1 and k, such that  $\delta_{k-1} \leq \delta'_{k-1}$  and  $\delta'_k < \delta_k$ . We can show that, by choosing  $\mathcal{P}'_k$  instead of  $\mathcal{P}_k$  at step k, the search could have produced a better partition plan. This contradicts the optimality of the DP algorithm. The full proof is included in Appendix A.

If the number of GPUs k is not a power of two, we factorize it to  $k = k_1 * k_2 * ... * k_m$ , where  $k_i \ge k_{i+1}$  for all i. At each step i in the recursive algorithm, we partition the dataflow graph into  $k_i$  workers in which each partition strategy still partitions a tensor along only one dimension but across  $k_i$  workers.

The benefits of recursion. Recursion dramatically cuts down the search time by partitioning along only one dimension at each step. For example, the number of configurations to be enumerated at each step for a 2D-convolution operator group is only  $4^6 = 4096$ . Therefore, the total number of partition strategies searched for the 2D-convolution operator.

Figure 3.7: (a) Original dataflow graph; (b) Partitioned graph with extra control dependencies (dashed lines).

tor with 8 workers (3 recursive steps) is 3\*4096, which is far fewer than  $20^6$  when recursion is not used. Table 3.1 shows the search time for two common large DNN models when applying the original DP algorithm on coarsened graph without and with recursion.

As another important benefit, recursion finds partition plans that work well with common hierarchical physical interconnects which have less aggregate bandwidth near the top of the hierarchy. For example, many commercial servers group GPUs by faster PCI-e buses first and then connect the groups with slower QPI buses or Infinibands. As theorem ?? indicates, Tofu assigns worker groups with less communication near the top of the hierarchical interconnects in earlier steps of the recursion.

## 3.6 Optimizations in generating the partitioned graph

Once the search algorithm determines how to partition for every tensor and operator, Tofu generates a corresponding partitioned dataflow graph. The graph generation process is mostly straightforward save for two optimizations, which are crucial to keep the perworker memory consumption low.